# **User Manual**

# MM32SPIN05x

# 32-bit Microcontroller Based on ARM Cortex M0 Core

Version: 1.19\_q

We reserve the right to change relevant information without notice.

## **Table of Contents**

| 1 | Men | nory and bus architecture                                    | 1  |

|---|-----|--------------------------------------------------------------|----|

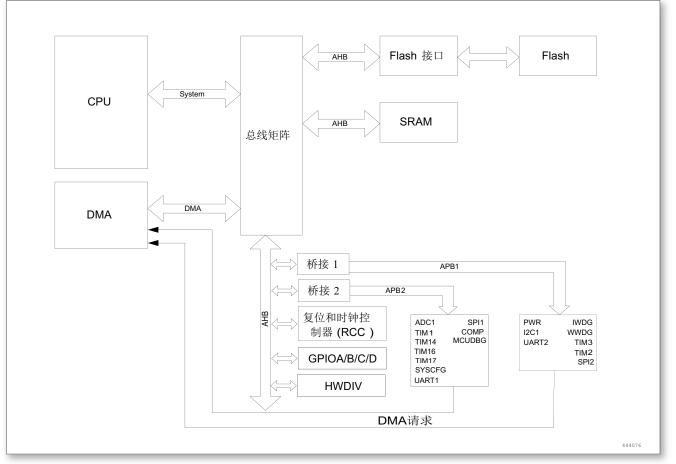

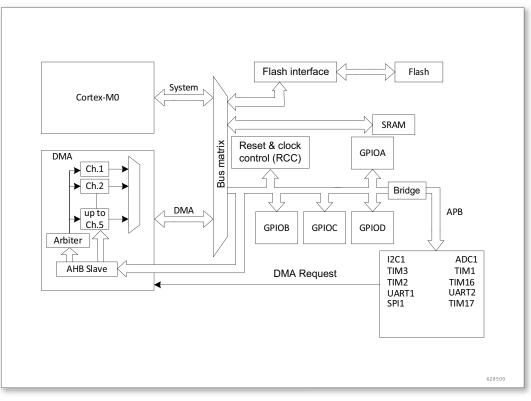

|   | 1.1 | System architecture                                          | 1  |

|   | 1.2 | Memory organization                                          | 2  |

|   |     | 1.2.1 Introduction                                           | 2  |

|   |     | 1.2.2 Memory map and register addressing                     | 2  |

|   | 1.3 | Embedded SRAM                                                | 4  |

|   | 1.4 | Overview of FLASH memory                                     | 4  |

|   | 1.5 | Boot configuration                                           | 5  |

| 2 | Emb | bedded flash(FLASH)                                          | 6  |

|   | 2.1 | Main features                                                | 6  |

|   | 2.2 | Functional description                                       | 6  |

|   |     | 2.2.1 Structure                                              | 6  |

|   |     | 2.2.2 Reading flash                                          | 7  |

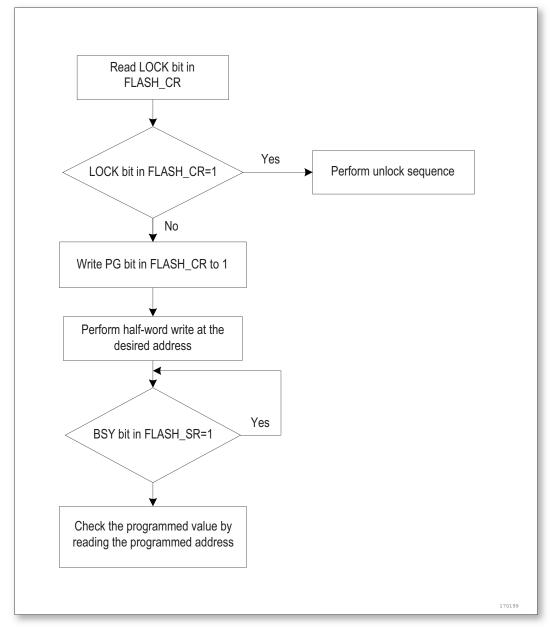

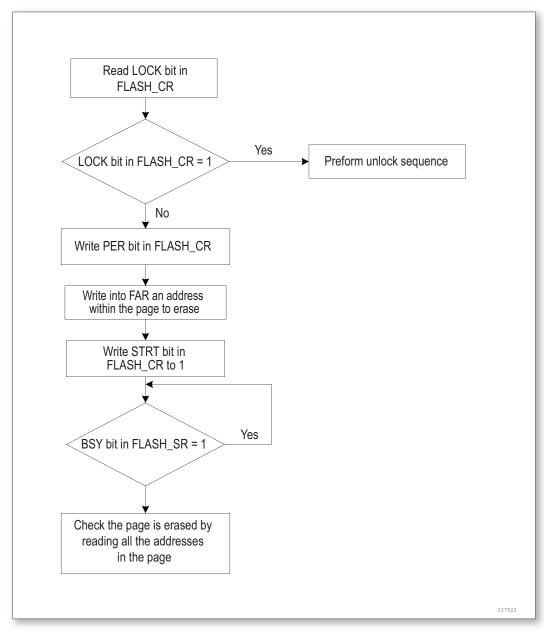

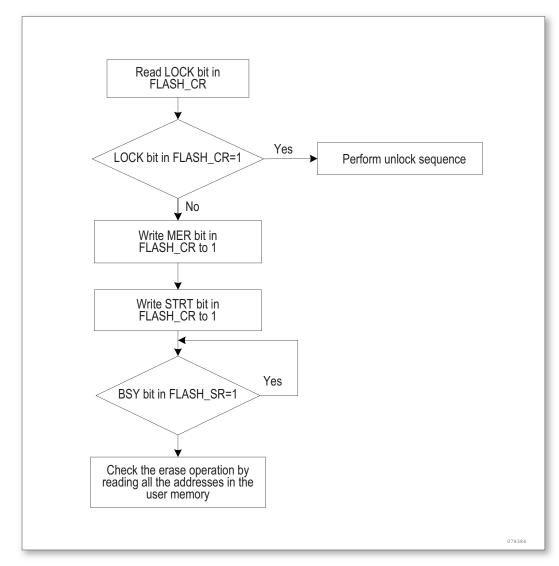

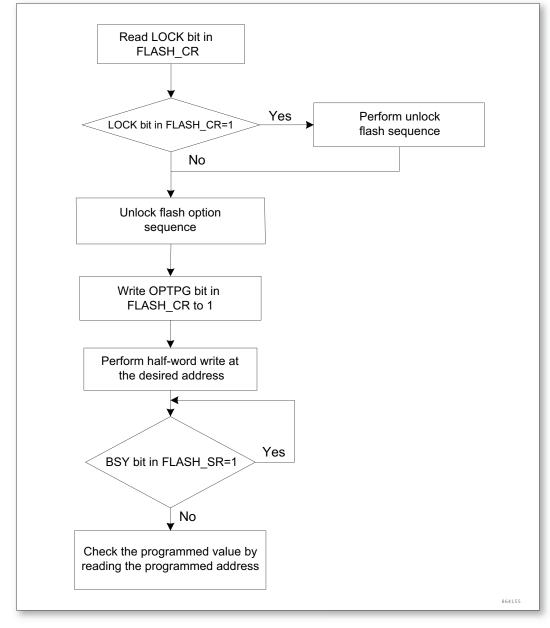

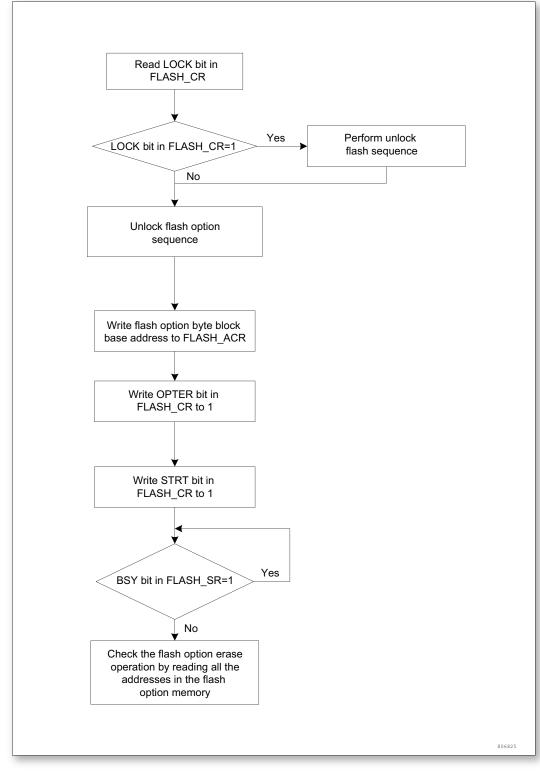

|   |     | 2.2.3 Programming and erasing flash                          | 8  |

|   | 2.3 | Storage protection                                           | 5  |

|   |     | 2.3.1 Write protection of main space                         | 5  |

|   |     | 2.3.2 Write protection of option bytes                       | 5  |

|   | 2.4 | Flash interrupt                                              | 5  |

|   | 2.5 | Description of option bytes                                  | 5  |

|   | 2.6 | Description of Flash register                                | 7  |

|   |     | 2.6.1 Flash access control register(FLASH_ACR)               | 8  |

|   |     | 2.6.2 Flash access control register(FLASH_KEYR)              | 8  |

|   |     | 2.6.3 Flash OPTKEY register(FLASH_OPTKEYR)                   | 9  |

|   |     | 2.6.4 Flash status register(FLASH_SR)                        | 9  |

|   |     | 2.6.5 Flash control register(FLASH_CR)                       | 20 |

|   |     | 2.6.6 Flash address register(FLASH_AR)                       | 21 |

|   |     | 2.6.7 Option byte register(FLASH_OBR)                        | 22 |

|   |     | 2.6.8 Write protection register(FLASH_WRPR)                  | 23 |

| 3 | Сус | lic redundancy check calculation unit(CRC) 2                 | 24 |

|   | 3.1 | CRC introduction                                             | 24 |

|   | 3.2 | CRC main features                                            | 24 |

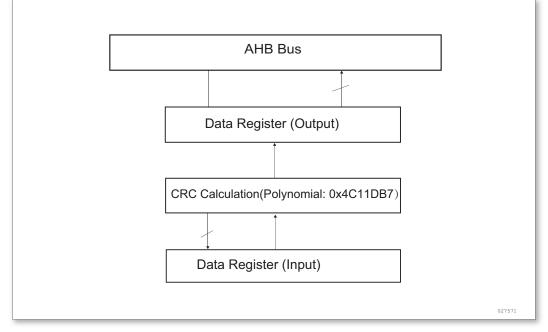

|   | 3.3 | CRC Functional description                                   | 25 |

|   | 3.4 | CRC register                                                 | 25 |

|   |     | 3.4.1 CRC data register(CRC_DR) 2                            | 25 |

|   |     | 3.4.2 CRC independent data register(CRC_IDR)                 | 26 |

|   |     | 3.4.3 CRC control register(CRC_CTRL)                         | 26 |

| 4 | Pow | ver control (PWR) 2                                          | 27 |

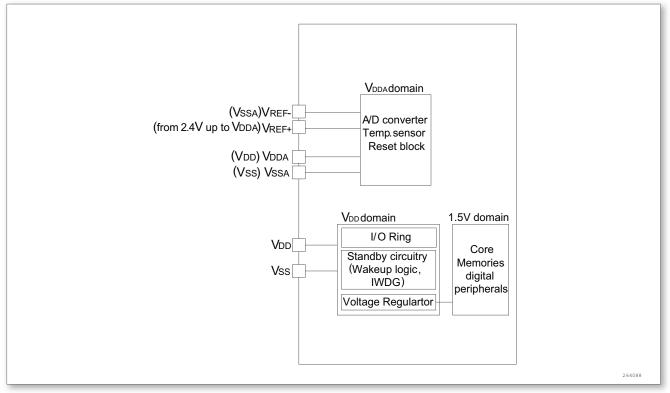

|   | 4.1 | Power supply                                                 | 27 |

|   |     | 4.1.1 Independent A/D converter supply and reference voltage | 27 |

|   |     | 4.1.2 Voltage regulator                                      | 28 |

|   | 4.2 | Power supply supervisor                                      | 28 |

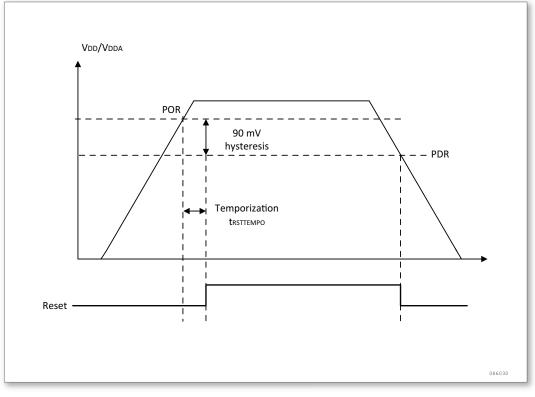

|   |      | 4.2.1    | Power on reset (POR)/power down reset (PDR)         | 28 |

|---|------|----------|-----------------------------------------------------|----|

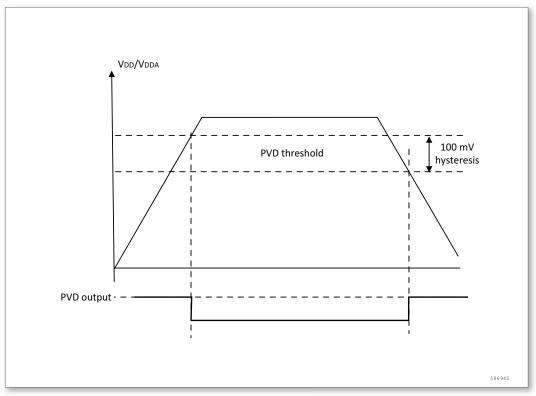

|   |      | 4.2.2    | Programmable voltage detector (PVD)                 | 28 |

|   | 4.3  | Low-po   | ower modes                                          | 29 |

|   |      | 4.3.1    | Slowing down system clocks                          | 31 |

|   |      | 4.3.2    | Peripheral clock gating                             | 31 |

|   |      | 4.3.3    | Sleep Mode                                          | 31 |

|   |      | 4.3.4    | Stop mode                                           | 32 |

|   |      | 4.3.5    | Standby mode                                        | 33 |

|   | 4.4  | Power    | control registers                                   | 34 |

|   |      | 4.4.1    | Power control registers(PWR_CR)                     | 35 |

|   |      | 4.4.2    | Power control/status register(PWR_CSR)              | 36 |

| 5 | Rese | et and c | clock control (RCC)                                 | 38 |

|   | 5.1  | Reset    |                                                     | 38 |

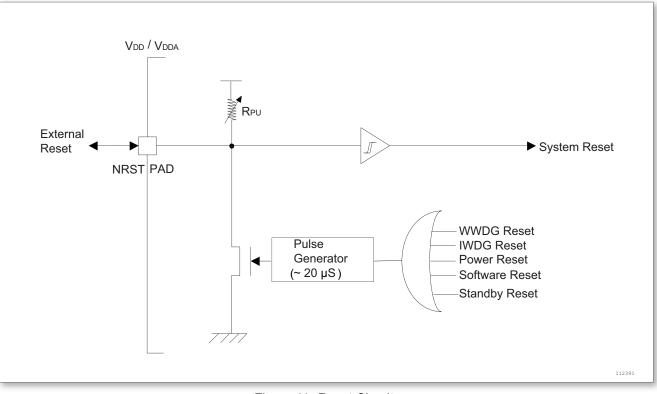

|   |      | 5.1.1    | System reset                                        | 38 |

|   |      | 5.1.2    | Power reset                                         | 38 |

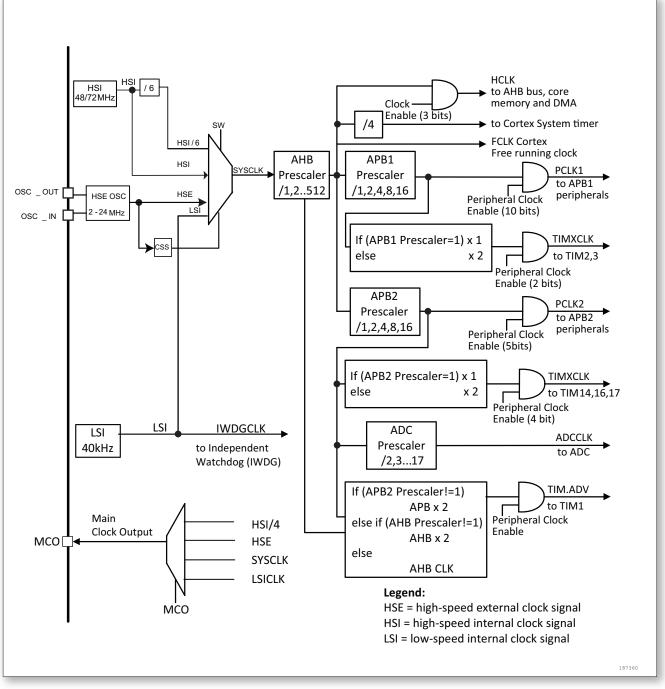

|   | 5.2  | Clocks   |                                                     | 39 |

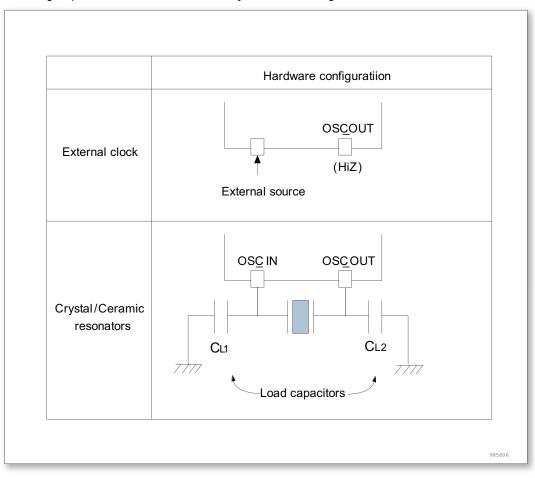

|   |      | 5.2.1    | HSE clock                                           | 41 |

|   |      | 5.2.2    | HSI clock                                           | 42 |

|   |      | 5.2.3    | LSI clock                                           | 42 |

|   |      | 5.2.4    | System clock (SYSCLK) selection                     | 43 |

|   |      | 5.2.5    | Clock security system (CSS)                         | 43 |

|   |      | 5.2.6    | Watchdog clock                                      | 43 |

|   |      | 5.2.7    | Clock-out capability                                | 43 |

|   | 5.3  | RCC R    | Register file and memory mapping description        | 43 |

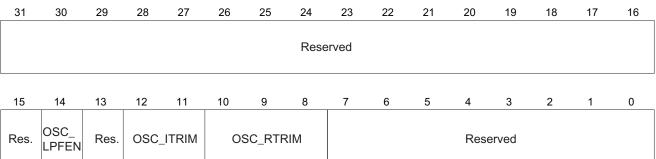

|   |      | 5.3.1    | Clock control register(RCC_CR)                      | 44 |

|   |      | 5.3.2    | Clock configuration register(RCC_CFGR)              | 46 |

|   |      | 5.3.3    | Clock interrupt register(RCC_CIR)                   | 48 |

|   |      | 5.3.4    | APB2 peripheral reset register(RCC_APB2RSTR)        | 50 |

|   |      | 5.3.5    | APB1 peripheral reset register(RCC_APB1RSTR)        | 51 |

|   |      | 5.3.6    | AHB peripheral clock enable register(RCC_AHBENR)    | 53 |

|   |      | 5.3.7    | APB2 peripheral clock enable register(RCC_APB2ENR)  | 54 |

|   |      | 5.3.8    | APB1 peripheral clock enable register (RCC_APB1ENR) | 55 |

|   |      | 5.3.9    | Control status register(RCC_CSR)                    | 56 |

|   |      | 5.3.10   | AHB peripheral clock reset register(RCC_AHBRSTR)    | 58 |

|   |      | 5.3.11   | System configuration register(RCC_SYSCFG)           | 59 |

| 6 | Gen  | eral-pu  | rpose I/O(GPIO)                                     | 61 |

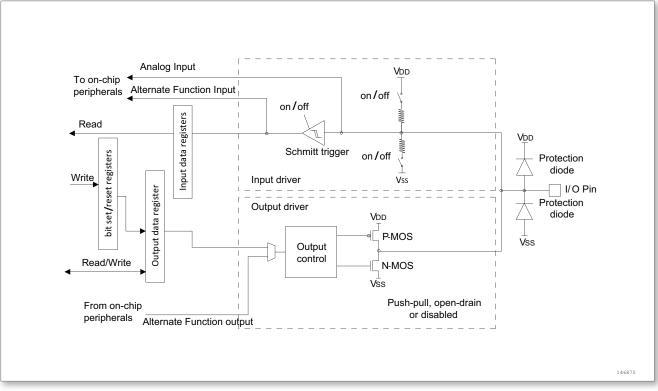

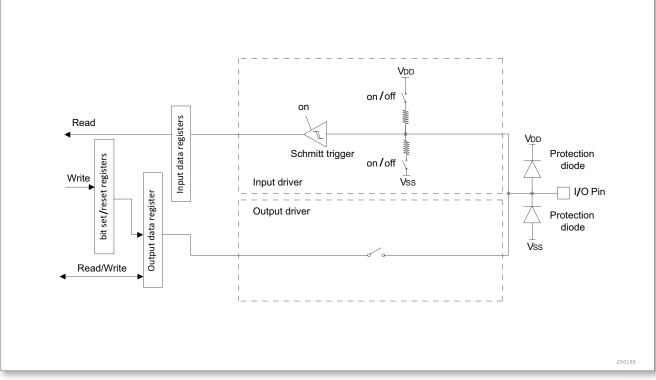

|   | 6.1  | GPIO f   | functional description                              | 61 |

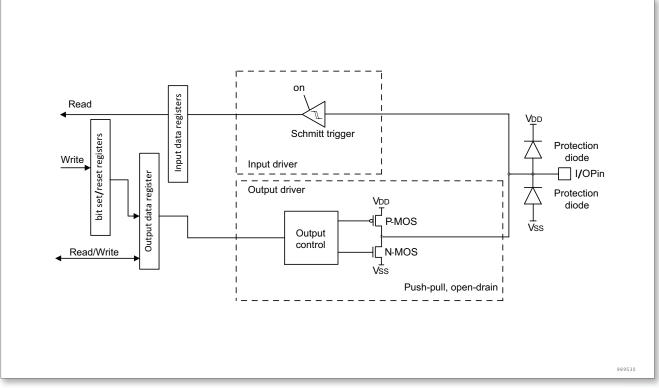

|   |      | 6.1.1    | General-purpose I/O(GPIO)                           | 62 |

|   |      | 6.1.2    | Atomic bits set or reset                            | 63 |

|   |      | 6.1.3    | External interrupt/wakeup lines                     | 63 |

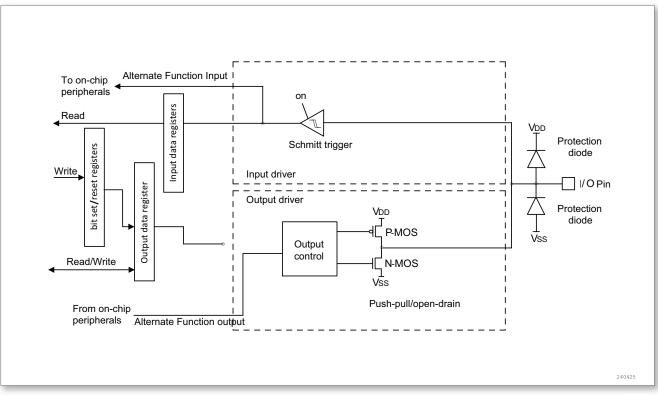

|   |      | 6.1.4    | Alternate functions                                 | 63 |

|   |      | 6.1.5    | Software remapping of I/O alternate functions       | 64 |

|   |      | 6.1.6    | GPIO locking mechanism                              | 64 |

|   |      |          |                                                     |    |

|   |       | 6.1.7   | Input configuration                                       | )4         |

|---|-------|---------|-----------------------------------------------------------|------------|

|   |       | 6.1.8   | Output configuration                                      | 35         |

|   |       | 6.1.9   | Alternate functions configuration                         | 35         |

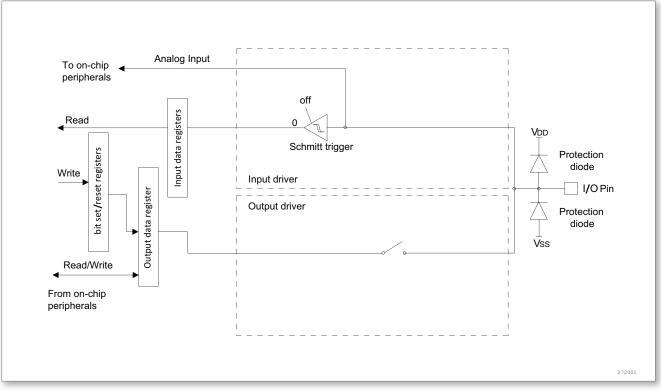

|   |       | 6.1.10  | Analog configuration                                      | 6          |

|   |       | 6.1.11  | GPIO configurations for device peripherals                | 37         |

|   | 6.2   | Alterna | ate function I/O and debug configuration (AFIO)           | 39         |

|   |       | 6.2.1   | Using OSC_IN/OSC_OUT pins as GPIO ports PD0/PD1           | 39         |

|   |       | 6.2.2   | SWD alternate function remapping                          | 39         |

|   | 6.3   | GPIO I  | register description                                      | 39         |

|   |       | 6.3.1   | Port configuration low register(GPIOx_CRL)(x = AD)        | <i>'</i> 0 |

|   |       | 6.3.2   | Port configuration high register(GPIOx_CRH)(x = AD)       | 1′         |

|   |       | 6.3.3   | Port input data register(GPIOx_IDR)(x = AD)7              | 71         |

|   |       | 6.3.4   | Port output data register(GPIOx_ODR)(x = AD)              | '2         |

|   |       | 6.3.5   | Port set/reset register(GPIOx_BSRR)(x = AD)               | '2         |

|   |       | 6.3.6   | Port bits reset register(GPIOx_BRR)(x = AD)               | 73         |

|   |       | 6.3.7   | Port configuration lock register(GPIOx_LCKR)(x = AD)      | ′3         |

|   |       | 6.3.8   | Port alternate-function register low(GPIOx_AFRL)(x = AD)  | 74         |

|   |       | 6.3.9   | Port alternate-function register high(GPIOx_AFRH)(x = AD) | ′5         |

| 7 | Inter | rupts a | nd events(EXTI) 7                                         | 77         |

|   | 7.1   | -       | Vectored Interrupt Controller                             | 77         |

|   |       | 7.1.1   | SysTick calibration value register                        |            |

|   |       | 7.1.2   | Interrupt and exception vectors                           | 7          |

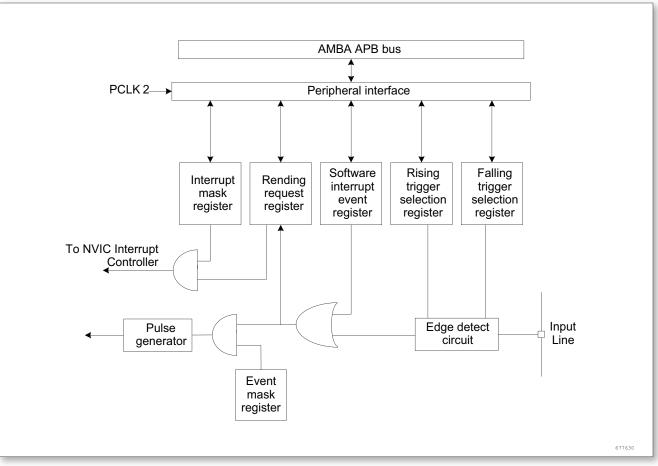

|   | 7.2   | Extern  | al interrupt/event controller (EXTI)                      | <i>'</i> 9 |

|   |       | 7.2.1   | Main features                                             | ′9         |

|   |       | 7.2.2   | Block diagram                                             | 30         |

|   |       | 7.2.3   | Wakeup event management                                   | 30         |

|   |       | 7.2.4   | Functional description                                    | 30         |

|   |       | 7.2.5   | External interrupt/event line mapping                     | 31         |

|   | 7.3   | EXTI r  | egister description                                       | 32         |

|   |       | 7.3.1   | Interrupt Mask Register(EXTI_IMR)                         | 33         |

|   |       | 7.3.2   | Event Mask Register(EXTI_EMR)                             | 33         |

|   |       | 7.3.3   | Rising Trigger Selection Register(EXTI_RTSR)              | 34         |

|   |       | 7.3.4   | Falling Trigger Selection Register(EXTI_FTSR)             | 35         |

|   |       | 7.3.5   | Software Interrupt Event Register(EXTI_SWIER)             | 36         |

|   |       | 7.3.6   | Pending register(EXTI_PR)                                 | 36         |

| 8 | Dire  | ct mem  | ory access controller(DMA)                                | 38         |

| - | 8.1   |         |                                                           | 38         |

|   | 8.2   |         | nain features                                             |            |

|   | 8.3   |         | onal description                                          |            |

|   |       | 8.3.1   | •                                                         | 39         |

|   |       | 8.3.2   |                                                           | 90         |

|   |       | 8.3.3   | DMA channels                                              |            |

|   |       | 8.3.4   | Programmable data width, data alignment and endians       |            |

|   |       |         |                                                           | -          |

|    |      | 8.3.5   | Error management                                              |

|----|------|---------|---------------------------------------------------------------|

|    |      | 8.3.6   | Interrupts                                                    |

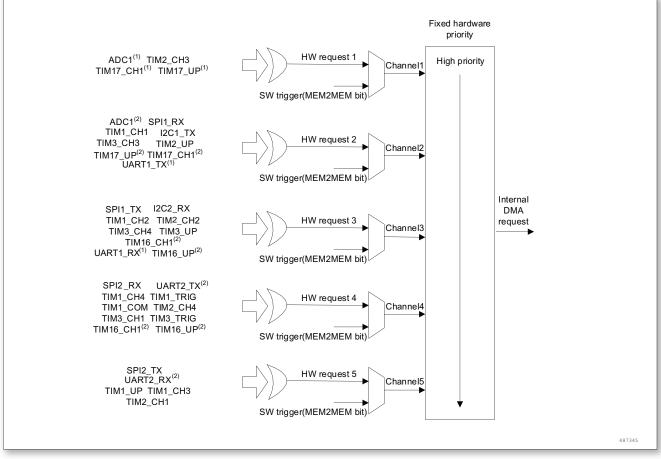

|    |      | 8.3.7   | DMA request mapping                                           |

|    | 8.4  | DMA re  | egister description                                           |

|    |      | 8.4.1   | DMA interrupt status register(DMA_ISR)                        |

|    |      | 8.4.2   | DMA interrupt flag clear register(DMA_IFCR)                   |

|    |      | 8.4.3   | DMA channel x configuration register(DMA_CCRx) (x = 1…5)      |

|    |      | 8.4.4   | DMA channel x number of data register(DMA_CNDTRx) (x = 15)    |

|    |      | 8.4.5   | DMA channel x peripheral address register(DMA_CPARx) (x = 15) |

|    |      | 8.4.6   | DMA channel x memory address register(DMA_CMARx) (x = 15)     |

| 9  | Anal | og-to-d | ligital converter(ADC) 102                                    |

|    | 9.1  | ADC in  | ntroduction                                                   |

|    | 9.2  | ADC m   | nain features                                                 |

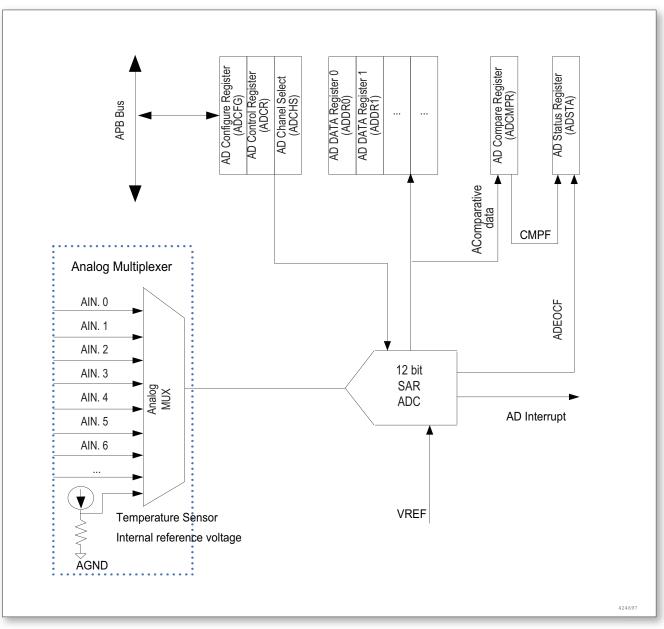

|    | 9.3  | ADC fu  | unctional description                                         |

|    |      | 9.3.1   | ADC on-off control                                            |

|    |      | 9.3.2   | Channel selection                                             |

|    | 9.4  | ADC o   | perating mode                                                 |

|    |      | 9.4.1   | Single conversion mode                                        |

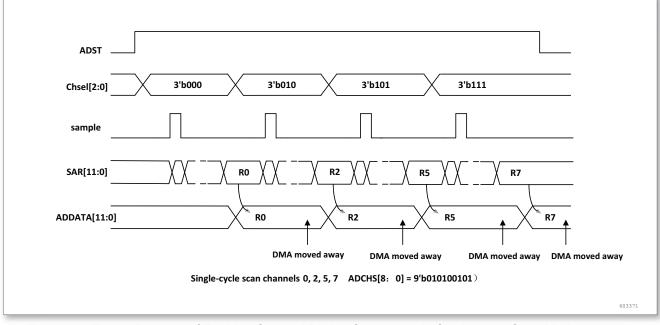

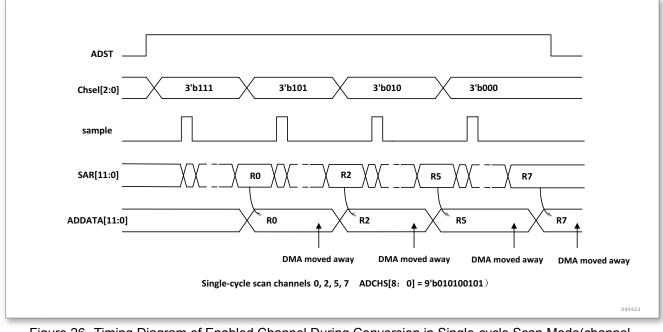

|    |      | 9.4.2   | Single-cycle scan mode                                        |

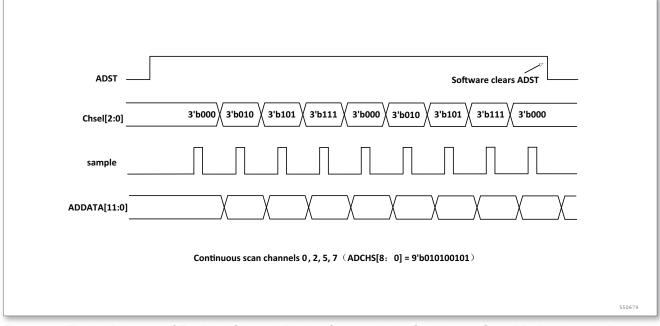

|    |      | 9.4.3   | Continuous scan mode                                          |

|    |      | 9.4.4   | DMA request                                                   |

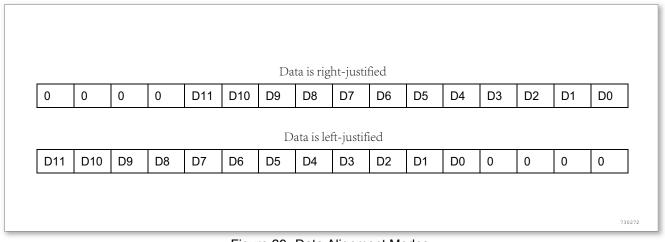

|    | 9.5  | Data a  | lignment                                                      |

|    |      | 9.5.1   | Programmable resolution                                       |

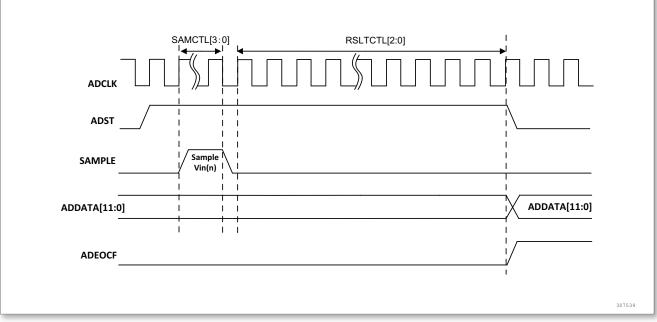

|    |      | 9.5.2   | Programmable sample time                                      |

|    | 9.6  |         | rsion on external trigger                                     |

|    | 9.7  | •       | rature sensor                                                 |

|    | 9.8  |         | al reference voltage                                          |

|    | 9.9  |         | ring of AD conversion results in window comparator mode       |

|    | 9.10 |         | egister description                                           |

|    |      |         | A/D data register(ADC_ADDATA)                                 |

|    |      |         | A/D configuration register(ADC_ADCFG)                         |

|    |      |         | A/D control register(ADC_ADCR)                                |

|    |      |         | A/D channel select register(ADC_ADCHS)                        |

|    |      |         | A/D window compare register(ADC_ADCMPR)                       |

|    |      |         | A/D status register(ADC_ADSTA)                                |

|    |      |         | A/D data register(ADC_ADDR0 ~ 12, 14 ~ 15)                    |

|    |      | 9.10.8  | A/D extended status register(ADC_ADSTA_EXT)                   |

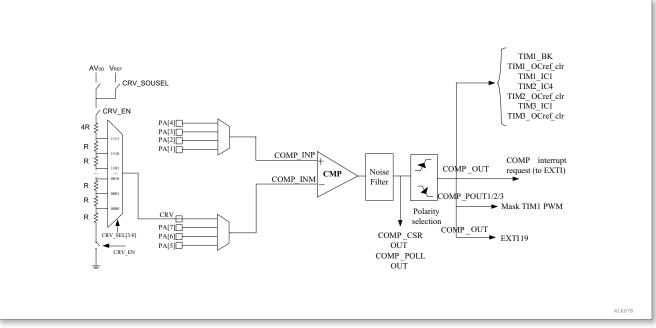

| 10 |      | -       | r(COMP) 121                                                   |

|    |      |         | introduction                                                  |

|    |      |         | eatures of comparator                                         |

|    | 10.3 |         | onal description of comparator                                |

|    |      |         | Introduction                                                  |

|    |      | 10.3.2  | Clock                                                         |

|    |      | 10.3.3 Comparator switch control                                |

|----|------|-----------------------------------------------------------------|

|    |      | 10.3.4 Comparator input and output                              |

|    |      | 10.3.5 Comparator channel selection                             |

|    |      | 10.3.6 Interrupt and wakeup                                     |

|    |      | 10.3.7 Power consumption mode                                   |

|    |      | 10.3.8 Comparator locking mechanism                             |

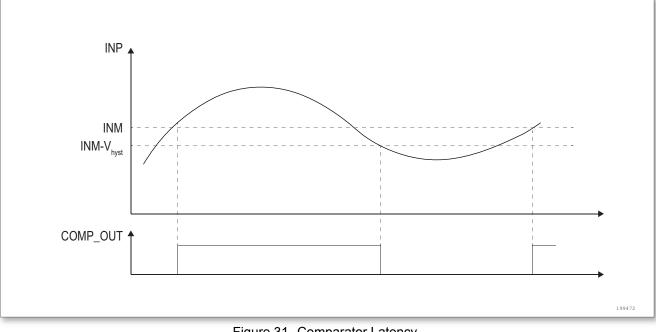

|    |      | 10.3.9 Latency                                                  |

|    | 10.4 | Description of comparator register                              |

|    |      | 10.4.1 Comparator control status register(COMPx_CSR)(x=1)       |

|    |      | 10.4.2 Comparator external reference voltage register(COMP_CRV) |

|    |      | 10.4.3 Comparator polling register(COMPx_POLL)(x=1)             |

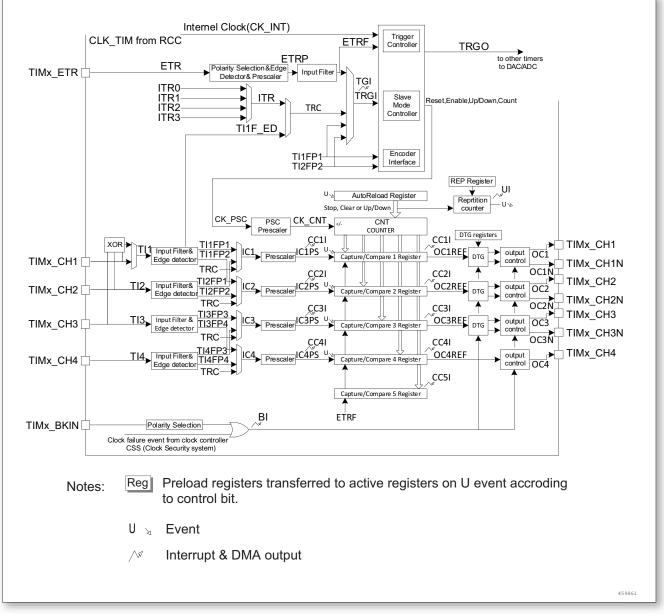

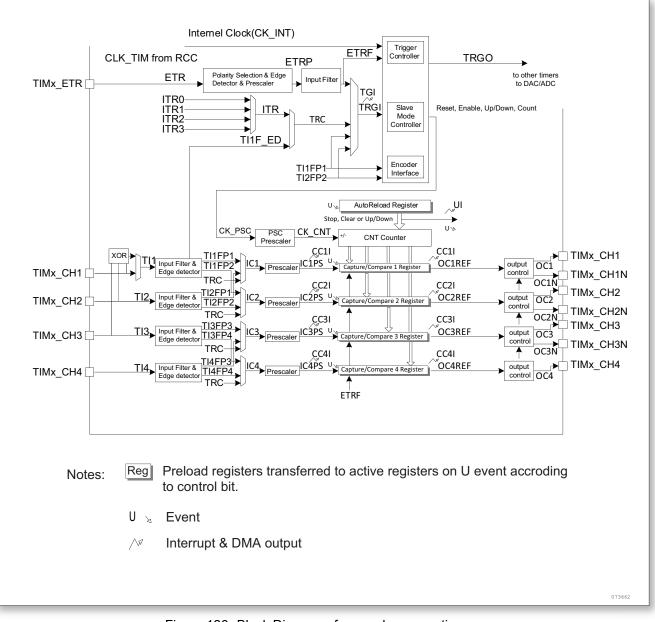

| 11 | Adva | anced-control timer(TIM1) 130                                   |

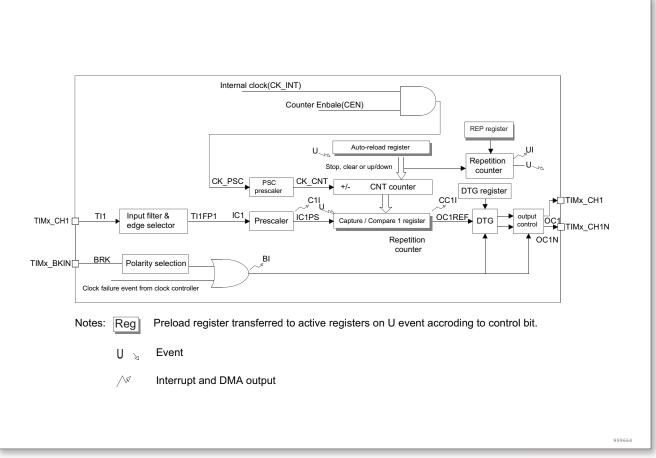

|    | 11.1 | TIM1 introduction                                               |

|    | 11.2 | Main features                                                   |

|    | 11.3 | Functional description                                          |

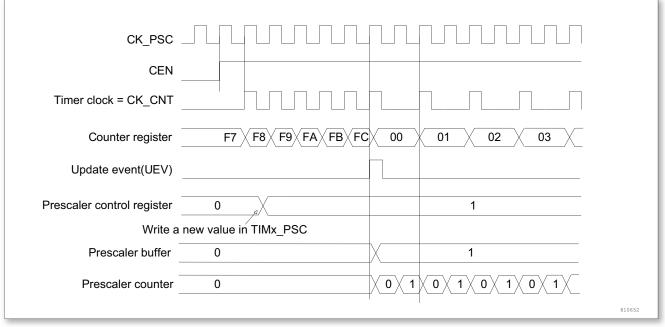

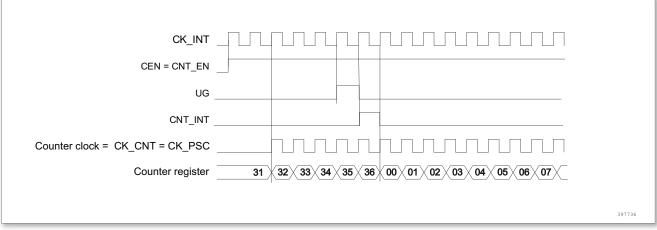

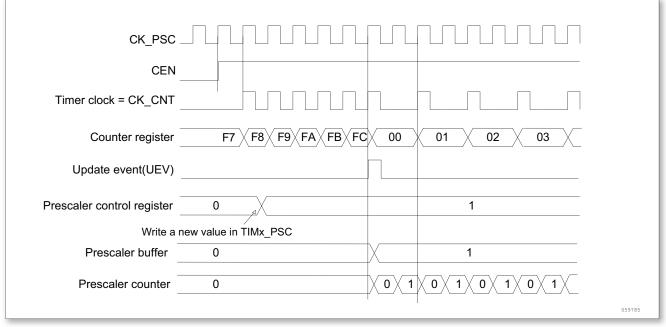

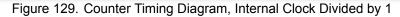

|    |      | 11.3.1 Time-base unit                                           |

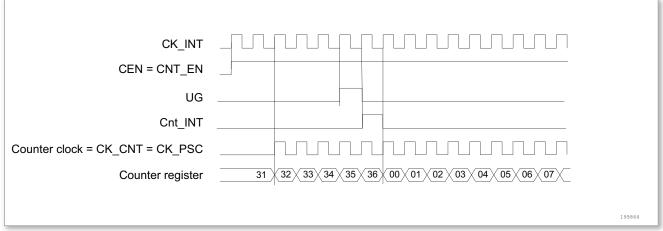

|    |      | 11.3.2 Counter modes                                            |

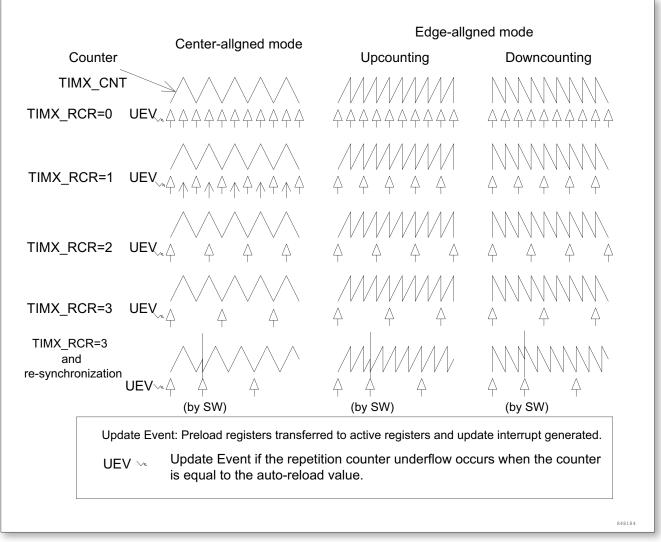

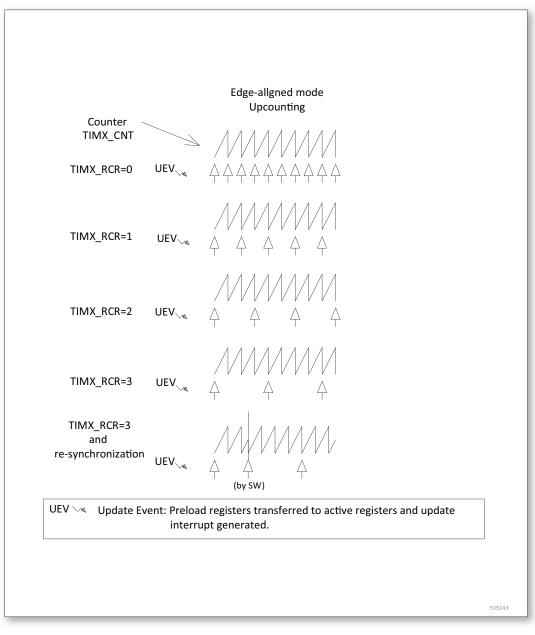

|    |      | 11.3.3 Repetition counter                                       |

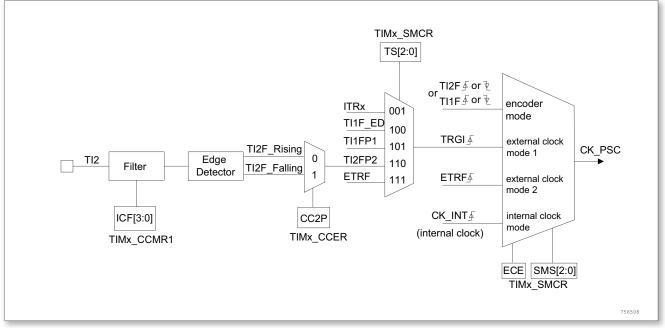

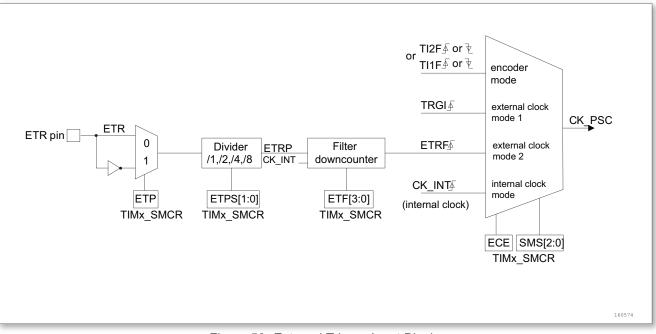

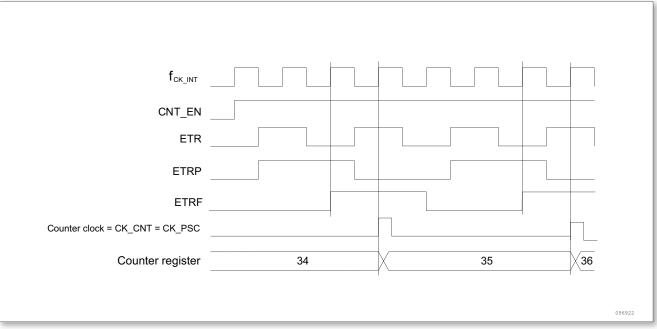

|    |      | 11.3.4 Clock selection                                          |

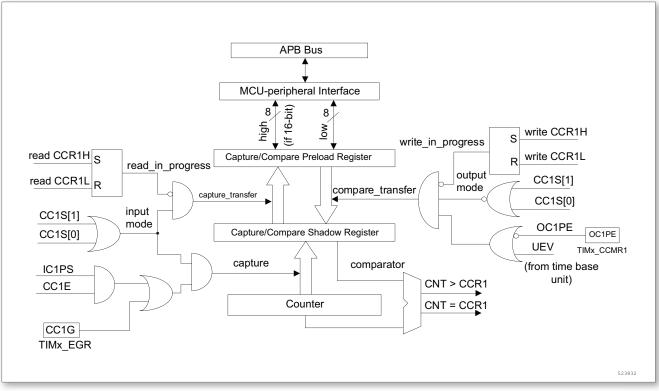

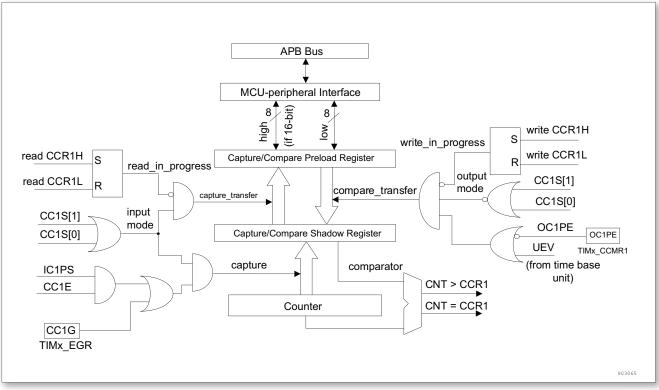

|    |      | 11.3.5 Capture/compare channels                                 |

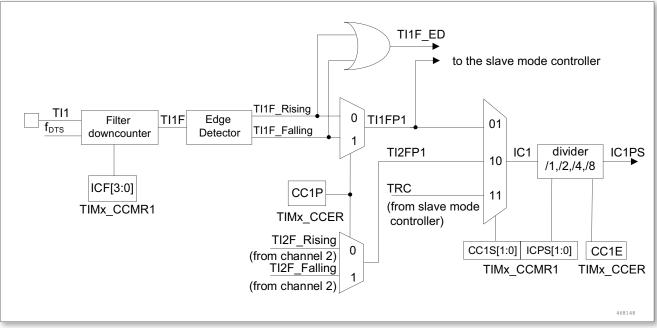

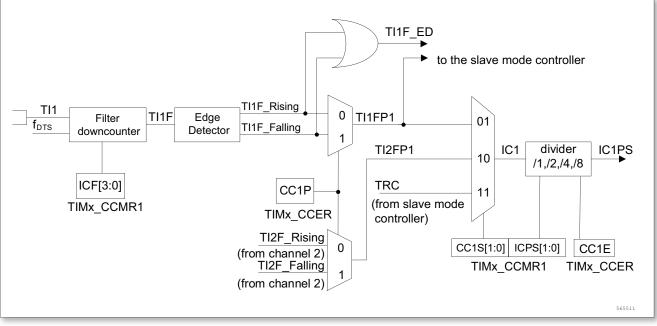

|    |      | 11.3.6 Input capture mode                                       |

|    |      | 11.3.7 PWM input mode                                           |

|    |      | 11.3.8 Forced output mode                                       |

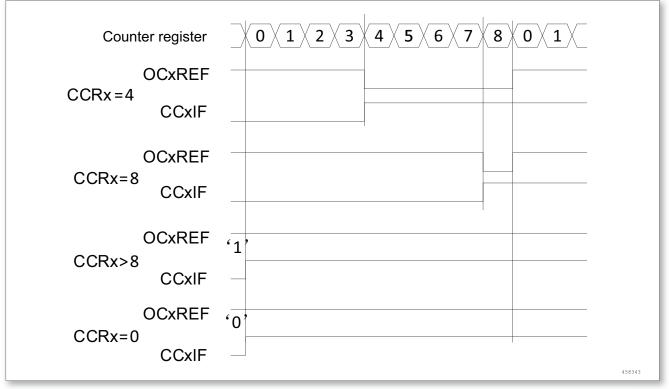

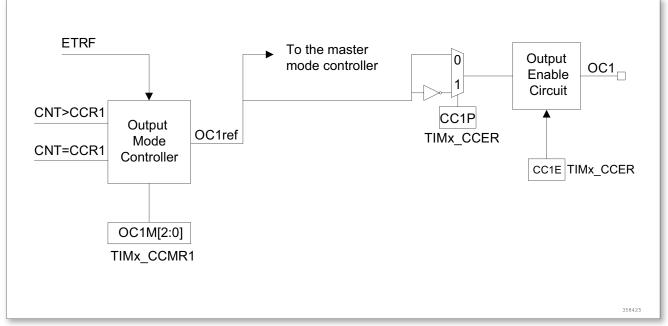

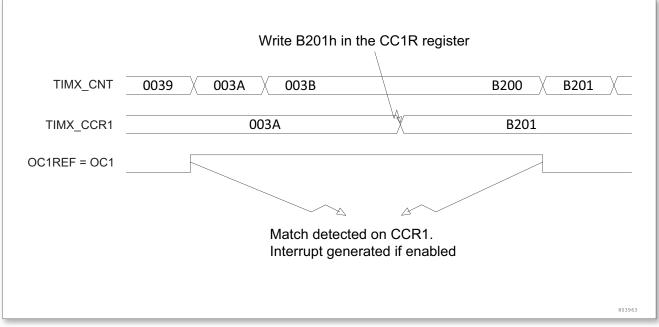

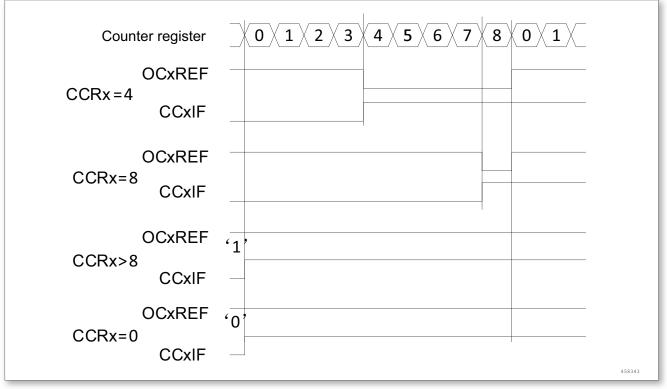

|    |      | 11.3.9 Output compare mode                                      |

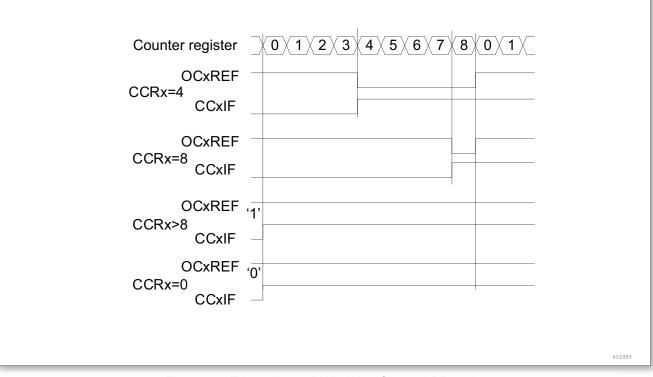

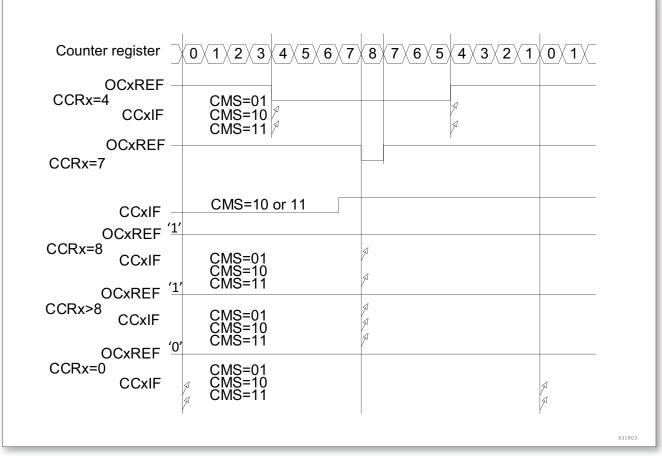

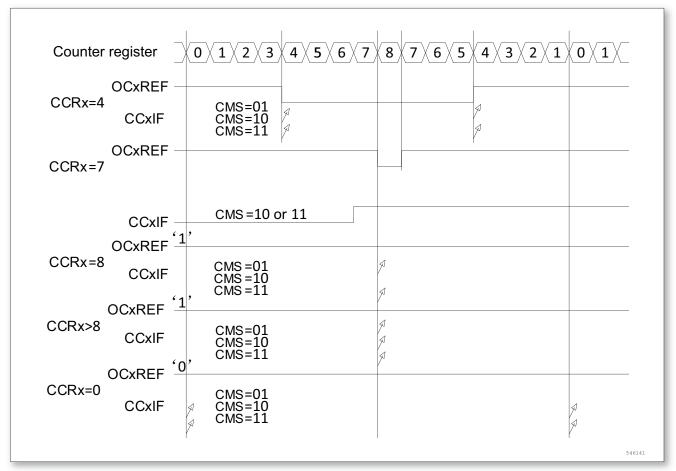

|    |      | 11.3.10 PWM mode                                                |

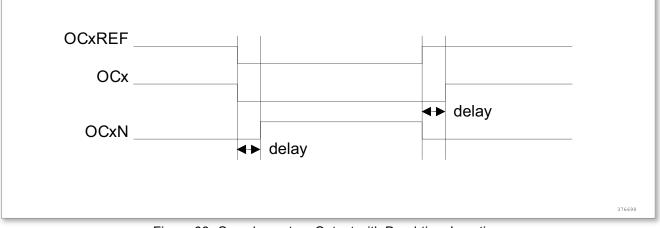

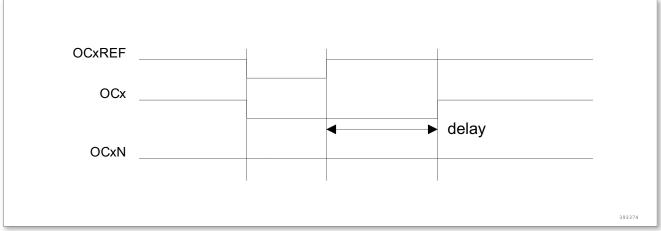

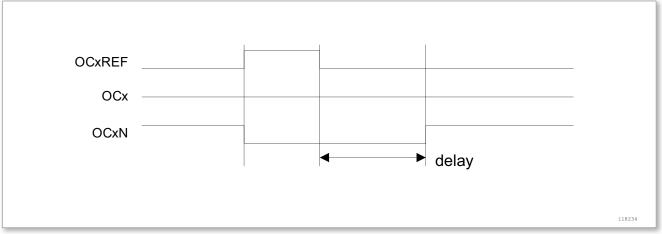

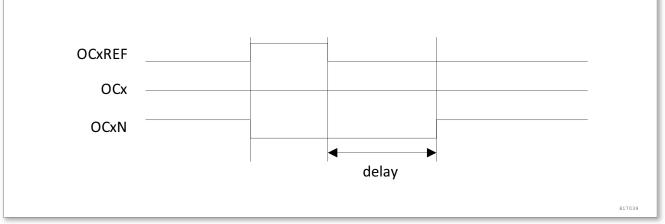

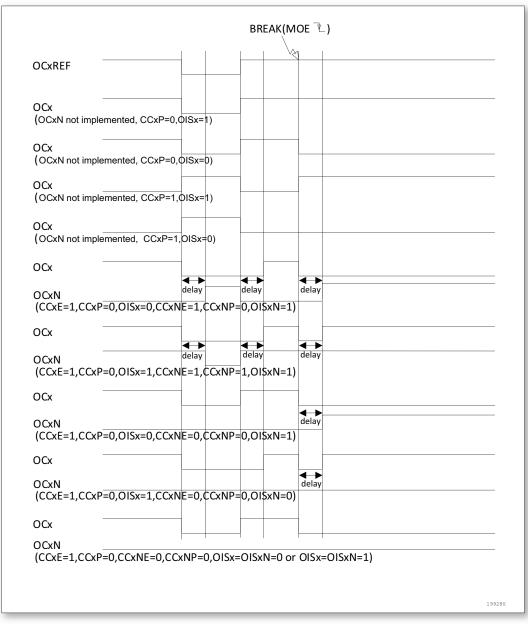

|    |      | 11.3.11 Complementary outputs and dead-time insertion           |

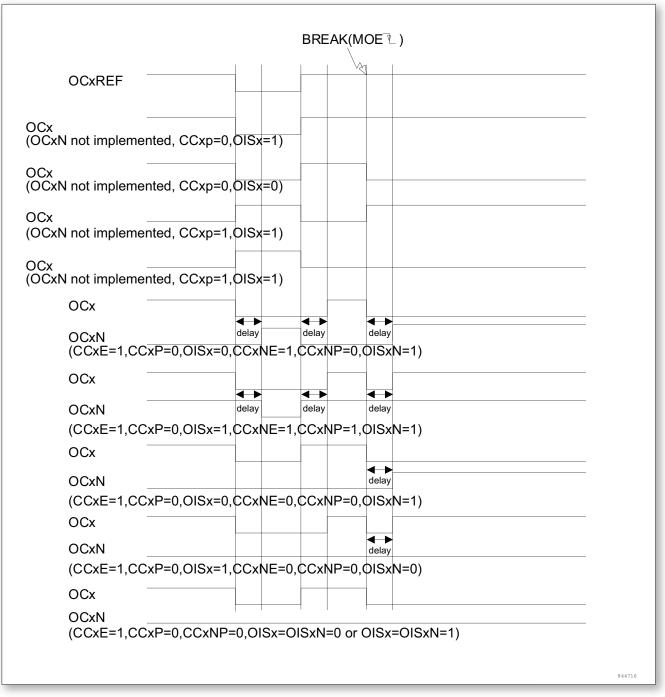

|    |      | 11.3.12 Using the break function                                |

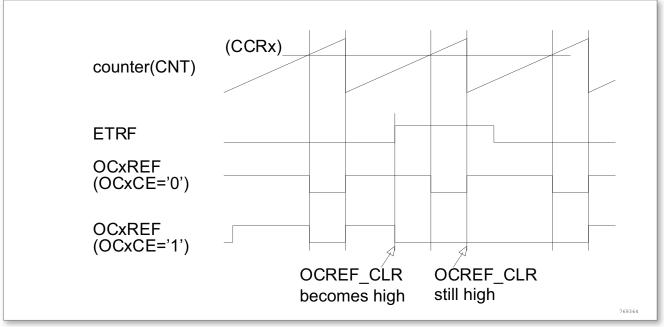

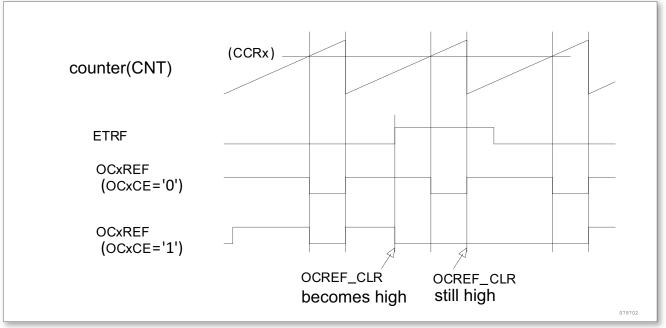

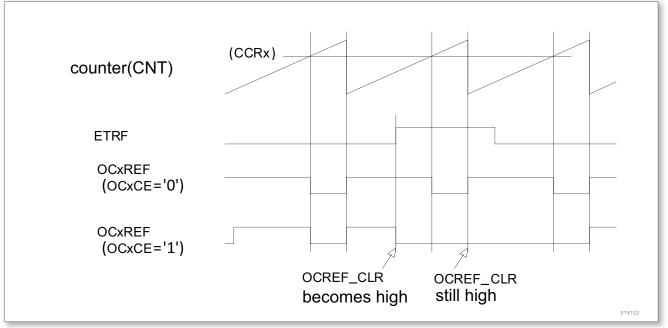

|    |      | 11.3.13 Clearing the OCxREF signal on an external event         |

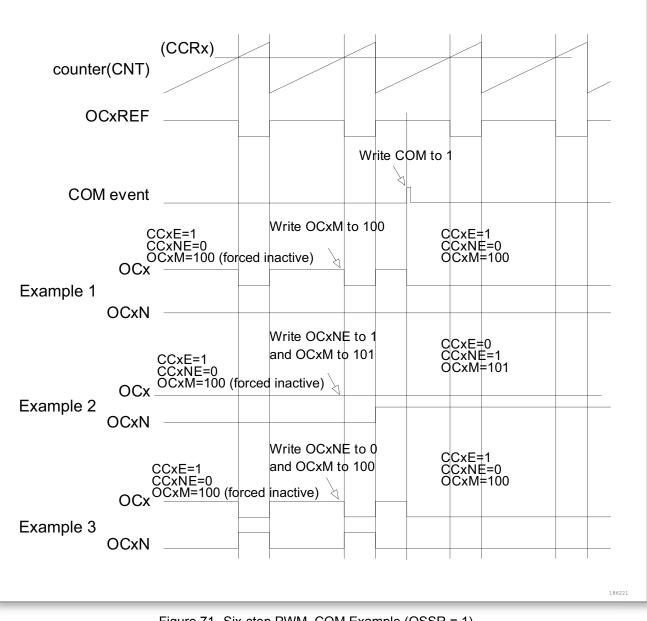

|    |      | 11.3.14 Six-step PWM generation                                 |

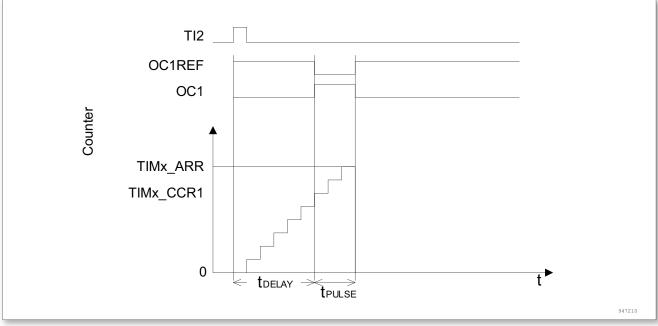

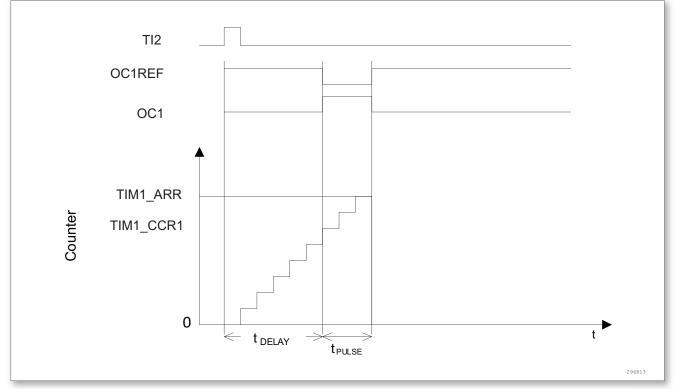

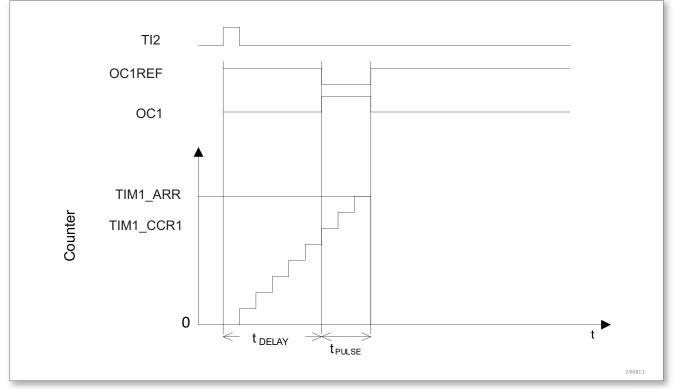

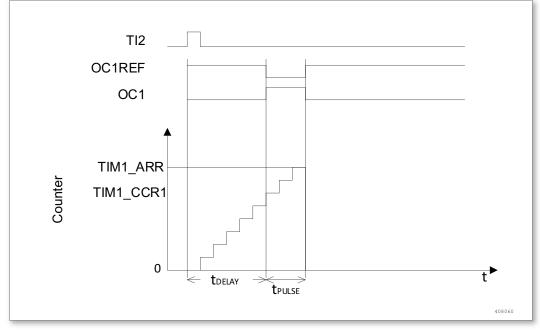

|    |      | 11.3.15 One-pulse mode                                          |

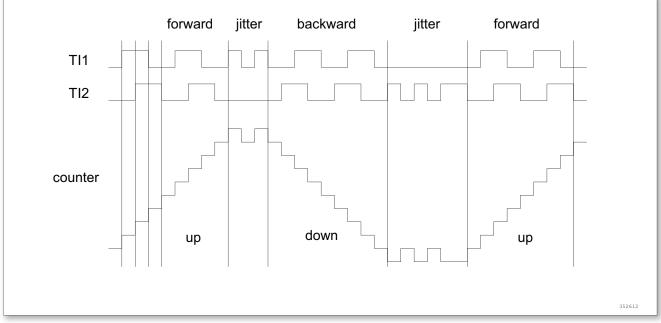

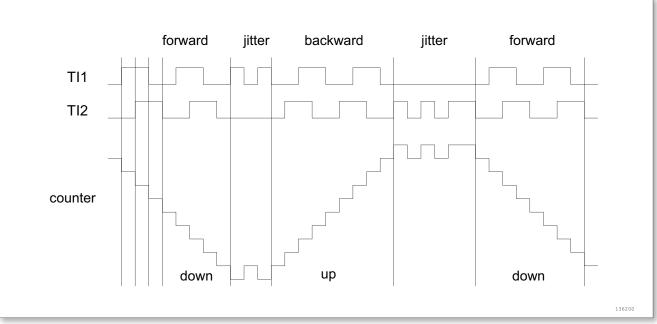

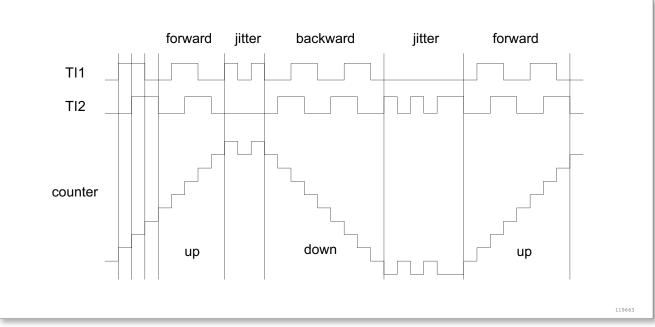

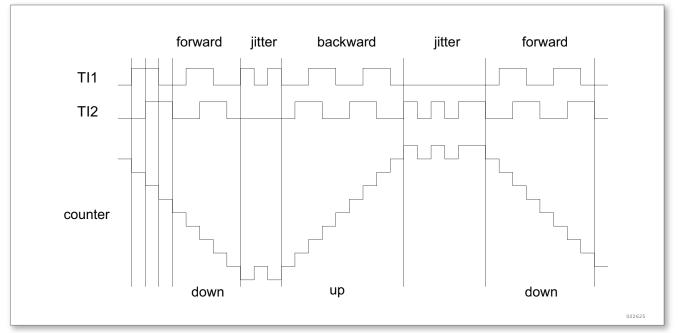

|    |      | 11.3.16 Encoder interface mode                                  |

|    |      | 11.3.17 Timer input XOR function                                |

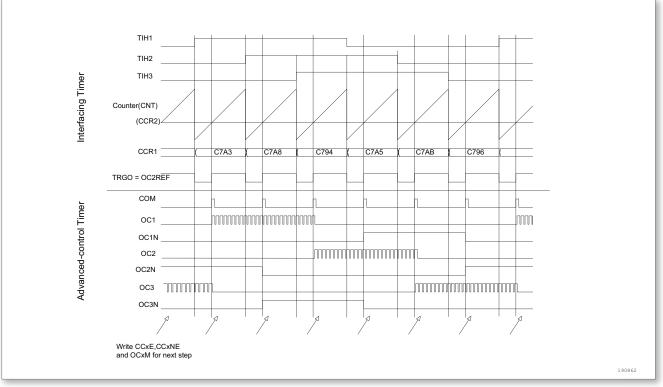

|    |      | 11.3.18 Interfacing with Hall sensors                           |

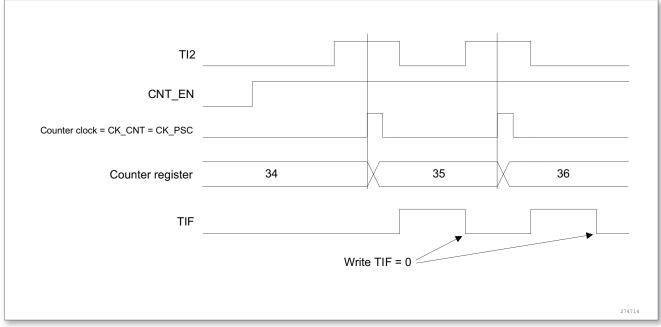

|    |      | 11.3.19 TIMx and external trigger synchronization               |

|    |      | 11.3.20 Timer synchronization                                   |

|    |      | 11.3.21 Debug mode                                              |

|    | 11.4 | Register description                                            |

|    |      | 11.4.1 Control register 1(TIMx_CR1)                             |

|    |      | 11.4.2 Control register 2(TIMx_CR2)                             |

|    |      | 11.4.3 Slave mode control register(TIMx_SMCR)                   |

|    |      | 11.4.4 DMA/interrupt enable register (TIMX_DIER)                |

|    |      | 11.4.5 Status register(TIMx_SR)                                 |

|    |      | 11.4.6 Event generation register (TIMx_EGR)                     |

|    |       | 11.4.7 Capture/compare mode register 1 (TIMx_CCMR1)18   | 37             |

|----|-------|---------------------------------------------------------|----------------|

|    |       | 11.4.8 Capture/compare mode register 2(TIMx_CCMR2)      | 92             |

|    |       | 11.4.9 Capture/compare enable register(TIMx_CCER)       | 94             |

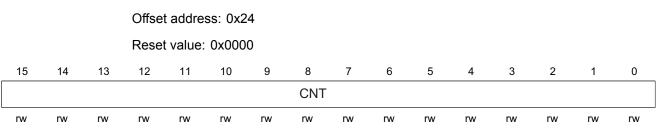

|    |       | 11.4.10 Counter(TIMx_CNT)                               | 98             |

|    |       | 11.4.11 Prescaler(TIMx_PSC)                             | 98             |

|    |       | 11.4.12 Auto-reload register(TIMx_ARR)                  | 98             |

|    |       | 11.4.13 Repetition counter register(TIMx_RCR)           | 99             |

|    |       | 11.4.14 Capture/compare register 1(TIMx_CCR1)           | 99             |

|    |       | 11.4.15 Capture/compare register2(TIMx_CCR2)            | 00             |

|    |       | 11.4.16 Capture/compare register 3(TIMx_CCR3)           | 00             |

|    |       | 11.4.17 Capture/compare register 4(TIMx_CCR4)           | )1             |

|    |       | 11.4.18 Break and dead-time register(TIMx_BDTR)         | )2             |

|    |       | 11.4.19 DMA control register(TIMx_DCR)                  | )5             |

|    |       | 11.4.20 DMA address for full transfer(TIMx_DMAR)        | )6             |

|    |       | 11.4.21 Capture/compare mode register 3(TIMx_CCMR3)     | )7             |

|    |       | 11.4.22 Capture/compare register 5(TIMx_CCR5)           | )7             |

| 12 | 16-bi | it general-purpose timers (TIMx16 Bit) 20               | 09             |

|    |       |                                                         |                |

|    |       | TIMx Main features                                      |                |

|    |       | TIMx Functional description                             |                |

|    |       | 12.3.1 Time-base unit                                   |                |

|    |       | 12.3.2 Counter modes                                    |                |

|    |       | 12.3.3 Clock selection                                  | 21             |

|    |       | 12.3.4 Capture/compare channels                         | 25             |

|    |       | 12.3.5 Input capture mode                               |                |

|    |       | 12.3.6 PWM input mode                                   | 28             |

|    |       | 12.3.7 Forced output mode                               | 29             |

|    |       | 12.3.8 Output compare mode                              | 29             |

|    |       | 12.3.9 PWM mode                                         |                |

|    |       | 12.3.10 One-pulse mode                                  | 34             |

|    |       | 12.3.11 Clearing the OCxREF signal on an external event | 35             |

|    |       | 12.3.12 Encoder interface mode                          | 36             |

|    |       | 12.3.13 Timer input XOR function                        | 39             |

|    |       | 12.3.14 Timers and external trigger synchronization     | 39             |

|    |       | 12.3.15 Timer synchronization                           | 42             |

|    |       | 12.3.16 Debug mode                                      | 47             |

|    | 12.4  | TIMx register description                               | 48             |

|    |       | 12.4.1 Control register 1(TIMx_CR1)                     | 48             |

|    |       |                                                         | . •            |

|    |       | 12.4.2 Control register 2(TIMx_CR2)                     |                |

|    |       |                                                         | 50             |

|    |       | 12.4.2 Control register 2(TIMx_CR2)                     | 50<br>52       |

|    |       | 12.4.2 Control register 2(TIMx_CR2)                     | 50<br>52<br>55 |

|    |       | 12.4.7 Capture/compare mode register 1(TIMx_CCMR1)      | . 259 |

|----|-------|---------------------------------------------------------|-------|

|    |       | 12.4.8 Capture/compare mode register 2(TIMx_CCMR2)      | . 264 |

|    |       | 12.4.9 Capture/compare enable register(TIMx_CCER)       | . 266 |

|    |       | 12.4.10 Counter(TIMx_CNT)                               | . 268 |

|    |       | 12.4.11 Prescaler(TIMx_PSC)                             | . 268 |

|    |       | 12.4.12 Auto-reload register(TIMx_ARR)                  | . 268 |

|    |       | 12.4.13 Capture/compare register 1(TIMx_CCR1)           | . 269 |

|    |       | 12.4.14 Capture/compare register2(TIMx_CCR2)            | . 269 |

|    |       | 12.4.15 Capture/compare register 3(TIMx_CCR3)           | . 270 |

|    |       | 12.4.16 Capture/compare register 4(TIMx_CCR4)           | . 270 |

|    |       | 12.4.17 DMA control register(TIMx_DCR)                  | . 271 |

|    |       | 12.4.18 DMA address for full transfer(TIMx_DMAR)        | . 272 |

| 13 | 32-bi | it general-purpose timers (TIMx32 Bit)                  | 274   |

|    | 13.1  | TIMx introduction                                       | . 274 |

|    |       | TIMx Main features                                      |       |

|    | 13.3  | TIMx Functional description                             | . 275 |

|    |       | 13.3.1 Time-base unit                                   |       |

|    |       | 13.3.2 Counter modes                                    | . 277 |

|    |       | 13.3.3 Clock selection                                  |       |

|    |       | 13.3.4 Capture/compare channels                         | . 290 |

|    |       | 13.3.5 Input capture mode                               |       |

|    |       | 13.3.6 PWM input mode                                   |       |

|    |       | 13.3.7 Forced output mode                               |       |

|    |       | 13.3.8 Output compare mode                              | . 294 |

|    |       | 13.3.9 PWM mode                                         | . 296 |

|    |       | 13.3.10 One-pulse mode                                  | . 299 |

|    |       | 13.3.11 Clearing the OCxREF signal on an external event |       |

|    |       | 13.3.12 Encoder interface mode                          |       |

|    |       | 13.3.13 Timer input XOR function                        |       |

|    |       | 13.3.14 Timers and external trigger synchronization     |       |

|    |       | 13.3.15 Timer synchronization                           | . 307 |

|    |       | 13.3.16 Debug mode                                      | . 312 |

|    | 13.4  |                                                         | . 313 |

|    |       | 13.4.1 Control register 1(TIMx_CR1)                     | . 313 |

|    |       | 13.4.2 Control register 2(TIMx_CR2)                     |       |

|    |       | 13.4.3 Slave mode control register(TIMx_SMCR)           | . 317 |

|    |       | 13.4.4 DMA/interrupt enable register(TIMx_DIER)         | . 320 |

|    |       | 13.4.5 Status register(TIMx_SR)                         | . 322 |

|    |       | 13.4.6 Event generation register(TIMx_EGR)              |       |

|    |       | 13.4.7 Capture/compare mode register 1(TIMx_CCMR1)      |       |

|    |       | 13.4.8 Capture/compare mode register 2(TIMx_CCMR2)      |       |

|    |       | 13.4.9 Capture/compare enable register(TIMx_CCER)       |       |

|    |       | 13.4.10 Counter(TIMx_CNT)                               |       |

|    |       |                                                         |       |

|    |      | 13.4.11 Prescaler(TIMx_PSC)                         |

|----|------|-----------------------------------------------------|

|    |      | 13.4.12 Auto-reload register(TIMx_ARR)              |

|    |      | 13.4.13 Capture/compare register 1(TIMx_CCR1)       |

|    |      | 13.4.14 Capture/compare register2(TIMx_CCR2)        |

|    |      | 13.4.15 Capture/compare register 3(TIMx_CCR3)       |

|    |      | 13.4.16 Capture/compare register 4(TIMx_CCR4)       |

|    |      | 13.4.17 DMA control register(TIMx_DCR)              |

|    |      | 13.4.18 DMA address for full transfer(TIMx_DMAR)    |

| 14 | Basi | c timer(TIM14) 339                                  |

|    | 14.1 | TIM14 introduction                                  |

|    | 14.2 | TIM14 Main features                                 |

|    | 14.3 | TIM14 Functional description                        |

|    |      | 14.3.1 Time-base unit                               |

|    |      | 14.3.2 Counter modes                                |

|    |      | 14.3.3 Repetition counter                           |

|    |      | 14.3.4 Clock source                                 |

|    |      | 14.3.5 Capture/compare channels                     |

|    |      | 14.3.6 Input capture mode                           |

|    |      | 14.3.7 Forced output mode                           |

|    |      | 14.3.8 Output compare mode                          |

|    |      | 14.3.9 PWM mode                                     |

|    |      | 14.3.10 Debug mode                                  |

|    | 14.4 | TIM14 register description                          |

|    |      | 14.4.1 Control register 1(TIM14_CR1)                |

|    |      | 14.4.2 Interrupt enable register(TIM14_DIER)        |

|    |      | 14.4.3 Status register(TIM14_SR)                    |

|    |      | 14.4.4 Event generation register(TIM14_EGR)         |

|    |      | 14.4.5 Capture/compare mode register 1(TIM14_CCMR1) |

|    |      | 14.4.6 Capture/compare enable register(TIM14_CCER)  |

|    |      | 14.4.7 Counter(TIM14_CNT)                           |

|    |      | 14.4.8 Prescaler(TIM14_PSC)                         |

|    |      | 14.4.9 Auto-reload register(TIM14_ARR)              |

|    |      | 14.4.10 Repetition counter register(TIM14_RCR)      |

|    |      | 14.4.11 Capture/compare register 1(TIM14_CCR1)      |

| 15 | Basi | c timer(TIM16/17) 363                               |

|    | 15.1 | TIM16/17 introduction                               |

|    | 15.2 | Main features                                       |

|    | 15.3 | Functional description                              |

|    |      | 15.3.1 Time-base unit                               |

|    |      | 15.3.2 Counting unit                                |

|    |      | 15.3.3 Repetition counter                           |

|    |      | 15.3.4 Clock source                                 |

|    |      | 15.3.5 Capture/compare channels                     |

|    |      |                                                     |

|    |                                                                                                                                          | 15.3.6 Input capture mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 373                                                                                                                                                                             |

|----|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                          | 15.3.7 Forced output mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 374                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.8 Output compare mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 375                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.9 PWM mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 376                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.10 Complementary outputs and dead-time insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 377                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.11 Using the break function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 379                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.12 One-pulse mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 381                                                                                                                                                                             |

|    |                                                                                                                                          | 15.3.13 Debug mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 383                                                                                                                                                                             |

|    | 15.4                                                                                                                                     | Register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 383                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.1 TIM16/17 control register 1(TIM16/17_CR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 383                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.2 TIM16/17 control register 2(TIM16/17_CR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 385                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.3 TIM16/17 interrupt enable register (TIM16/17_DIER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 386                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.4 TIM16/17 interrupt enable register(TIM16/17_SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 387                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.5 TIM16/17 event generation register 1(TIM16/17_EGR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 388                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.6 TIM16/17 capture/compare mode register 1(TIM16/17_CCMR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 390                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.7 TIM16/17 Capture/compare enable register(TIM16/17_CCER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 394                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.8 TIM16/17 counter(TIM16/17_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 396                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.9 TIM16/17 prescaler register(TIM16/17_PSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 397                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.10 TIM16/17 auto-reload register(TIM16/17_ARR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 397                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.11 TIM16/17 repetition counter register(TIM16/17_RCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 397                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.12 TIM16/17 Capture/compare register 1(TIM16/17_CCR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 398                                                                                                                                                                             |

|    |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                   |

|    |                                                                                                                                          | 15.4.13 TIM16/17 break and dead-time register(TIM16/17_BDTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 398                                                                                                                                                                             |

|    |                                                                                                                                          | 15.4.13 TIM16/17 break and dead-time register(TIM16/17_BDTR)15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                   |

|    |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 401                                                                                                                                                                             |

| 16 | Inde                                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401                                                                                                                                                                             |

| 16 |                                                                                                                                          | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b>                                                                                                                                                      |

| 16 | 16.1                                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b><br>. 404                                                                                                                                             |

| 16 | 16.1<br>16.2                                                                                                                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404                                                                                                                                    |

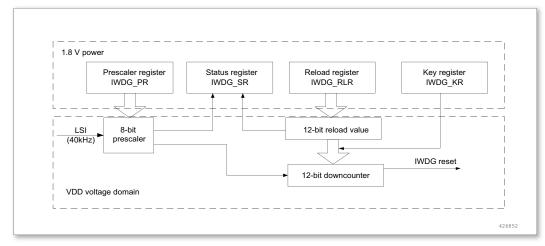

| 16 | 16.1<br>16.2                                                                                                                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)       15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)       15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)       1000 (IWDG introduction)         IWDG main features       1000 (IWDG introduction)                                                                                                                                                                                                                                                                                                                                                                                      | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404                                                                                                                           |

| 16 | 16.1<br>16.2                                                                                                                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)       15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)       15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)       1000 mitroduction         (IWDG introduction)       1000 min features         Functional description       1000 min features                                                                                                                                                                                                                                                                                                                                          | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404<br>. 405                                                                                                                  |

| 16 | 16.1<br>16.2                                                                                                                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404<br>. 405<br>. 405                                                                                                         |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404<br>. 405<br>. 405<br>. 406                                                                                                |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404<br>. 405<br>. 405<br>. 406<br>. 406                                                                                       |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)       15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)       16.000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 401<br>402<br>404<br>404<br>404<br>405<br>405<br>405<br>406<br>406                                                                                                                |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)       15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)       (IWDG introduction)         (IWDG main features       10.11 features         Functional description       16.3.1 Hardware watchdog         16.3.2 Register access protection       16.3.3 Debug mode         IWDG register description       16.4.1 Key register(IWDG_KR)                                                                                                                                                                                                                                                                                                                               | 401<br>402<br>404<br>404<br>404<br>404<br>405<br>405<br>405<br>406<br>406<br>406                                                                                                  |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.2 Prescaler register(IWDG_PR)                                                                                                                                                                                                                                                                                                | 401<br>402<br>404<br>404<br>404<br>405<br>405<br>406<br>406<br>406<br>406                                                                                                         |

| 16 | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.3 Reload register(IWDG_RLR)                                                                                                                                                                                                                                                                                                  | 401<br>402<br>404<br>404<br>404<br>404<br>405<br>405<br>406<br>406<br>406<br>406<br>406<br>406                                                                                    |

|    | 16.1<br>16.2<br>16.3                                                                                                                     | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.2 Prescaler register(IWDG_PR)         16.4.3 Reload register(IWDG_SR)         16.4.4 Status register(IWDG_SR)         16.4.5 IWDG Control register(IWDG_CR)                                                                                                                                                                  | 401<br>402<br>404<br>404<br>404<br>404<br>405<br>405<br>406<br>406<br>406<br>406<br>406<br>406                                                                                    |

|    | 16.1<br>16.2<br>16.3<br>16.4                                                                                                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.2 Prescaler register(IWDG_RR)         16.4.3 Reload register(IWDG_RLR)         16.4.4 Status register(IWDG_SR)         16.4.5 IWDG Control register(IWDG_CR)                                                                                                                                                                 | . 401<br>. 402<br><b>404</b><br>. 404<br>. 404<br>. 404<br>. 405<br>. 405<br>. 406<br>. 406<br>. 406<br>. 406<br>. 407<br>. 408<br>. 409<br><b>410</b>                            |

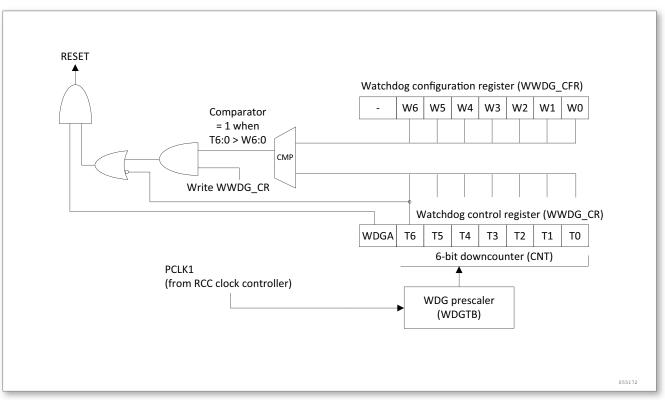

|    | <ul> <li>16.1</li> <li>16.2</li> <li>16.3</li> <li>16.4</li> <li>Wind</li> <li>17.1</li> </ul>                                           | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.2 Prescaler register(IWDG_PR)         16.4.3 Reload register(IWDG_RLR)         16.4.4 Status register(IWDG_SR)         16.4.5 IWDG Control register(IWDG_CR)         WWDG introduction                                                                                                                                       | 401<br>402<br>404<br>404<br>404<br>405<br>405<br>405<br>406<br>406<br>406<br>406<br>406<br>406<br>407<br>408<br>409<br>410                                                        |

|    | <ul> <li>16.1</li> <li>16.2</li> <li>16.3</li> <li>16.4</li> <li>Winc</li> <li>17.1</li> <li>17.2</li> </ul>                             | 15.4.14 TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15 TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1 Hardware watchdog         16.3.2 Register access protection         16.3.3 Debug mode         IWDG register description         16.4.1 Key register(IWDG_KR)         16.4.2 Prescaler register(IWDG_PR)         16.4.3 Reload register(IWDG_RLR)         16.4.4 Status register(IWDG_SR)         16.4.5 IWDG Control register(IWDG_CR)         WWDG introduction         WWDG introduction         WWDG main features                                                                                  | 401<br>402<br>404<br>404<br>404<br>404<br>405<br>405<br>405<br>406<br>406<br>406<br>406<br>407<br>408<br>409<br>410<br>410                                                        |

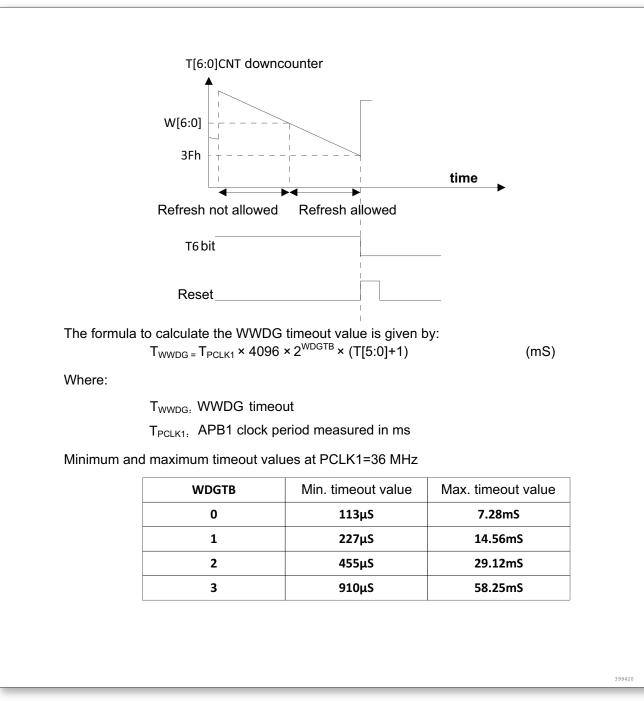

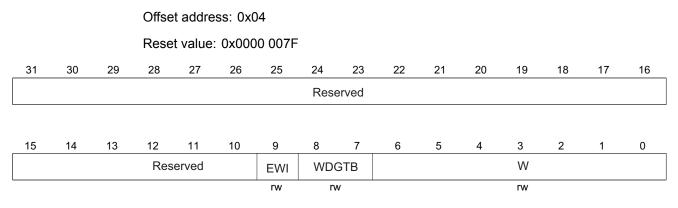

|    | <ul> <li>16.1</li> <li>16.2</li> <li>16.3</li> <li>16.4</li> <li>Wind</li> <li>17.1</li> <li>17.2</li> <li>17.3</li> </ul>               | 15.4.14       TIM16/17 DMA DMA control register(TIM16/17_DCR)         15.4.15       TIM16/17 address for full transfer(TIM16/17_DMAR)         pendent watchdog(IWDG)         (IWDG introduction)         IWDG main features         Functional description         16.3.1         Hardware watchdog         16.3.2         Register access protection         16.3.3         Debug mode         IWDG register description         16.4.1         Key register(IWDG_KR)         16.4.2         Prescaler register(IWDG_PR)         16.4.3         Reload register(IWDG_RLR)         16.4.4         Status register(IWDG_SR)         16.4.5         IWDG control register(IWDG_CR)         WWDG introduction         WWDG main features         Functional description | 401<br>402<br>404<br>404<br>404<br>405<br>405<br>406<br>406<br>406<br>406<br>406<br>406<br>406<br>407<br>408<br>409<br>410<br>410<br>410                                          |