## Using Lattice's ispLever Starter Software

This document is a "how to" on producing JEDEC files for GALs using Verilog.

Leif Ilvedson April 28, 2002

Revision 1: Joe Barta July 8, 2002

Revision 2: James K. Peckol September 8, 2005

#### Overview

The following is a procedure on the basic use of Lattice's ispLever Starter Software in conjunction with Synplicity's Synplify software.

#### Scope

The scope of the following procedure is to produce a JEDEC file for the target PLD, the GAL22V10D-15LP, using Verilog. This tutorial will leave you with the ability to produce JEDECs for either the GAL22V10 or GAL16V8 along with their different versions (referring to their suffixes: A, B, C, D, -15LP, -25LP, etc).

A BCD-to-7-segment-decoder implemented using a GAL16V8D will be used to demonstrate the design process.

#### Estimated Time to Completion: 20 minutes

#### **Big Picture**

You will first use Lattice's ispLSS (ispLever Starter Software) to set up your project then import your Verilog code (.v). Then you'll use the softwareto produce a .jed (JEDEC) file. The JEDEC file is what will be used to program your GAL.

#### Strategy

If you make no pin assignments, ispLSS will automatically make pin assignments for you. This is an expletive-saver, especially if your design is complex and uses most of the pins. The pin assignments ispLSS makes are optimal for your design. Use this to your advantage:

- 1) When you are finished writing your Verilog code, let ispLSS automatically assign pins for you.

- 2) Take those pin assignments and hard-code them. That way, if you need to make any changes in your code, the pin assignments won't change and therefore you won't have to do any rewiring.

#### Understanding the Procedure Protocol

The following protocol may be seen: go to **File/New Project**. This implies that one would click on the **File** menu, then on **New Project** button. Duh.

### Procedure

- 1. Start the ispLever Starter Software.

- 2. Go to File/New Project. This will start the Project Wizard

3. In the *Design Entry Type* menu, select **Schematic/Verilog HDL** as in Figure 1.

| roject Wizard                               |            |                   |          | 2    |

|---------------------------------------------|------------|-------------------|----------|------|

| Project <u>N</u> ame: Ur                    | ntitled    |                   |          |      |

| Location:                                   |            |                   |          |      |

|                                             | e\verilog\ |                   |          | []   |

| Design Entry <u>T</u> ype:                  |            | <u>S</u> ynthesis | s Tools: |      |

| Schematic/ABEL<br>Schematic/VHDL<br>VHDL    |            | Synplify          |          |      |

| Schematic/Verilog HD<br>Verilog HDL<br>EDIF | DL         |                   |          |      |

| GDF                                         |            |                   |          |      |

|                                             |            |                   |          |      |

|                                             |            |                   |          |      |

|                                             |            |                   |          |      |

|                                             | < Back     | <u>N</u> ext >    | Cancel   | Help |

|                                             |            | <u>Next</u>       |          |      |

Figure 1.

- 4. Give the project a title by selecting the *Project Name* block of the Project Wizard window as shown in Figure 2. Enter "Comparitor0".

- 5. Give the project a location by selecting the *Location* block of the Project Wizard window as shown in Figure 2. Enter or browse to the desired location. Click **Next**.

| Project Wizard                           | X                        |

|------------------------------------------|--------------------------|

| Project <u>N</u> ame: Comparitor0        |                          |

| Location:                                |                          |

| D:\UW\UW\271\CODE\VERILOG\COMPA          | RITORI),                 |

| Design Entry <u>T</u> ype:               | <u>S</u> ynthesis Tools: |

| Schematic/ABEL<br>Schematic/VHDL<br>VHDL | Synplify                 |

| Schematic/Verilog HDL<br>Verilog HDL     |                          |

| EDIF<br>GDF                              |                          |

|                                          |                          |

|                                          |                          |

|                                          |                          |

| ·                                        |                          |

| < Back                                   | Next > Cancel Help       |

Figure 2.

6. Now the target device needs to be selected. *Under Select Device Family*, scroll up to **GAL Device** in the left pane of the Project Wizard window.

In the Select Device window (Figure 3), select the appropriate choice from the drop-down menu. In this example, we use GAL16V8D. Then select the Speed grade and Package type.

Click Next.

| Select Device:<br>Eamily:<br>GAL Device<br>GAL Device                                                              | Device:<br>GAL16V8D<br>GAL16V8D                                          | Device Informatio<br>Status:<br>Density:   | Production<br>- |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|-----------------|

| ispGDX Device<br>ispGDX2 Device<br>ispGDX2-E Device<br>ispLEVER Default Dev<br>ispLSI XC Device<br>ispLSI S000VE ▼ | GAL16V8Z<br>GAL16V8ZD<br>GAL16V98B<br>GAL18V10<br>GAL18V10B<br>GAL20LV8D | Logic cells:<br>VO cells:<br>VO pins:      | -<br>8<br>8     |

| Speed grade: (ns)                                                                                                  | Package type:<br>20PDIP<br>Power:<br>Low                                 | Dedicated input:<br>Output enable:<br>Icc: | 8<br>1<br>90 mA |

| GAL16V8D-15LP                                                                                                      | <u></u>                                                                  | Show <u>O</u> bsolete                      | Devices         |

Figure 3.

7. Select the Add Source button and browse to the appropriate \*.v file.

| oject Wizard - Add Sour  | ce          |           |        |      |

|--------------------------|-------------|-----------|--------|------|

| Add Source               |             | emove     |        |      |

| Source Files:            |             |           |        |      |

| File                     |             | Source Ty | /pe    |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

| F. Comu Rouwoo to Work F | live etc. v |           |        |      |

| Copy Source to Work E    | niectory    |           |        |      |

|                          |             |           |        |      |

|                          |             |           |        |      |

|                          | < Back      | Next >    | Cancel | Help |

|                          | Dack        | LIGK()    | Cancer | heip |

Figure 4.

8. Select the desired file and select *Open* as in Figure 5

| Import File: (S        | Schematic/Verilog HDL)  | ?×           |

|------------------------|-------------------------|--------------|

| Look <u>i</u> n: 🔂     | Comparitor0 💽 🕂 🗈 📸 🎫   | •            |

| comparitor             | 0.                      |              |

|                        |                         |              |

|                        |                         |              |

|                        |                         |              |

|                        |                         |              |

| File <u>n</u> ame:     | comparitor0.∨           | <u>O</u> pen |

| Files of <u>t</u> ype: | Sources (.txt,.sch;.v;) | Cancel       |

| r neo ortype.          |                         | //           |

Figure 5.

The comparator code appears in the following listing,

| /**********                                             | ***************************************                              |

|---------------------------------------------------------|----------------------------------------------------------------------|

| * Title:                                                | Sample Verilog source code A Simple Comparitor                       |

| <ul> <li>* Model type</li> <li>* Description</li> </ul> |                                                                      |

| *                                                       | of a greater than comparison                                         |

| * Programm                                              |                                                                      |

| * Date:                                                 | Date typed                                                           |

| ********                                                | ***************************************                              |

|                                                         |                                                                      |

| // Define the                                           | Comparitor module                                                    |

| module Com                                              | paritor(greater, a, b, c, d);                                        |

| // within the                                           | modules, wires are impliedwe can put them in if we want to           |

| output                                                  | greater; // Ouputs: greater                                          |

| input                                                   | a, b, c, d; // Inputs: to compare, ab and cd                         |

|                                                         |                                                                      |

| // This i                                               | s a structural model                                                 |

|                                                         |                                                                      |

|                                                         | e building a gate level model with propagation delay                 |

| // YOL                                                  | J DO NOT HAVE TO TYPE THESE COMMENT LINES.                           |

| // Gate                                                 | instantiation format:                                                |

|                                                         | e-of-module #(prop. delay) assigned-name (outputs-list, inputs_list) |

|                                                         |                                                                      |

| and<br>and                                              | and1(term0, a, notC);<br>and2(term1, b, notC, notD);                 |

| and                                                     | and3(term2, a, b, notD);                                             |

|                                                         |                                                                      |

| not                                                     | inv0(notC, c);                                                       |

| not                                                     | inv1(notD,d);                                                        |

| or                                                      | or1(greater, term0, term1, term2);                                   |

| endmodule                                               | //close Comparitor module                                            |

|                                                         |                                                                      |

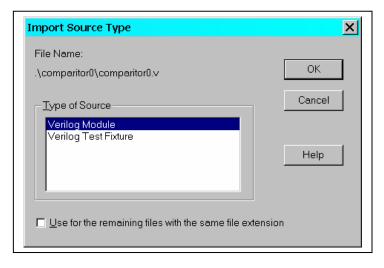

9. Select *Verilog Module* when the *Import Source Type* window pops open as in Figure 6. Select **OK**

10. Click Next.

|                                         | Verilog Module |                            |

|-----------------------------------------|----------------|----------------------------|

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

|                                         |                |                            |

| ork Directory                           |                |                            |

| , i i i i i i i i i i i i i i i i i i i |                |                            |

|                                         |                |                            |

|                                         | ork Directory  | Source Type Verilog Module |

## 11. Click Finish.

| Project Wizard - Project Information                                                                                                                                                                                    | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| The new project will be generated with the following specifications:                                                                                                                                                    |   |

| Project:<br>Project Name: Comparitor0<br>Project Title: Comparitor0<br>Project Location: D\/UW\UW\271\CODE\\VERILOG\COMPARITOR0\<br>Project Type: Schematic/Verilog HDL<br>Device: GAL16V8D-15LP<br>Synthesis: Synplify |   |

| Sources:<br>Verilog Module:<br>d:\uw\uw\271\code\∨erilog\comparitor0\comparitor0.∨                                                                                                                                      |   |

| I<br>< <u>B</u> ack Finish Cancel Help                                                                                                                                                                                  |   |

Figure 8.

- isplever Project Navigator [D:\UW\...\CODE\VERILOG\COMPARITOR0\Comparitor0.syn] \_ 🗆 🗙 File View Source Process Options Tools Window Help 🗅 😅 🖬 🛛 Normal 🔻 🕸 🔏 😭 100 CD 🔲 🖼 🙀 💆 💡 📢 Sources in Project: Processes for current source: Link Design Comparitor0 Documents GAL 16V8D-15LP 🖸 Fit Desian Comparitor (comparitor0.v) Pre-Fit Equations Verilog Variables Post-Fit Equations 🗎 Fitter Report 🚺 Signal Cross Reference Create Fuse Map 🗎 Chip Report 🗎 JEDEC File G Verilog Post-Route Simulation Model UHDL Post-Route Simulation Model ispLEVER Auto-Make Log File ٠ Updating: Hierarchy Start to record tcl script... Finished recording TCL script. Starting: 'C:\ispTOOLS5\_0\_STRT\ispcpld\bin\vlog2jhd.exe "comparitor0.v" -p "c:\ispTOOLS5\_0\_STRT\ispcp Done: completed successfully. Automake Log / 😒 🔕 » │ ﷺ Clo.... 🔯 Cal.... 🐼 Œu... 🚺 My... 🔄 D:.... 👘 Usi... 👘 isp.... 👘 Usi... 🕵 Ve... 🕅 Iab... | 54:0V0.

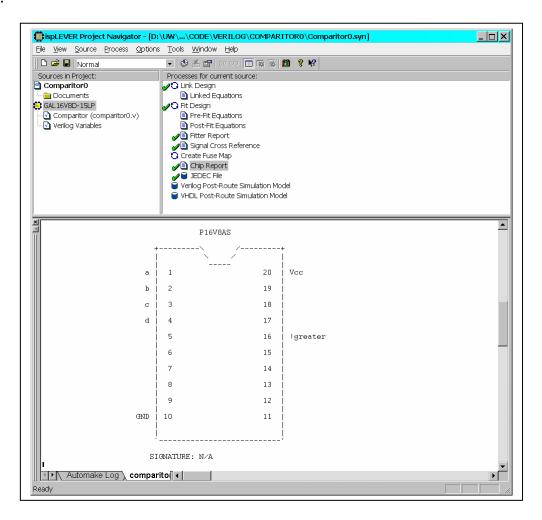

- 12. The Project Wizard exits to the Project Navigator screen as in Figure 9.

Figure 9.

#### Side Note (Controlling the pin assignments):

To have control over the pin assignments, you must declare the pin assignments in comments after you have declared the input or output variable. The format for a pin assignment declaration that is an input goes as follows (note: the X in PX is the pin number of the chip):

```

input <variable name> /* synthesis LOC= "PX" */

```

and likewise the format for a pin assignment declaration that is an output goes as follows:

output <variable> /\* synthesis LOC="PX" \*/

The format for multiple pin assignments is as follows (note: once again X and Z are just pin numbers they can be any number you want):

input [n:0] <variable name> /\* synthesis LOC= "Pn X....PoZ" \*/

and likewise the format for a pin assignment declaration that is an output goes as follows:

output [n:0] <variable name> /\* synthesis LOC= "P<sub>n</sub> X....P<sub>0</sub>Z" \*/

Here are some more examples of pin assignments:

Ex. 1 (input variable "flag" at pin 3):

input flag /\* synthesis LOC="P3" \*/;

EX. 2 (Two output variables: carrryOut at pin 5 and barrowOut at pin 6):

output carryOut /\* synthesis LOC="P17" \*/, borrowOut /\* synthesis LOC="P18"\*/;

# Note: if you do not put a space between the variable and the comment, Synplify (the compiler) will give you a warning.

13. To produce the JEDEC file, select the target chip in the *Sources in Project* pane and then double-click "**JEDEC File**" in the *Process for Current Sources* pane.

Your *Process for Current Sources* pane should now look like that in Figure 10. The JEDEC file has been created and you're ready to take it to the programmer! You're finished!

| ispLEVER Project Navigator - [D:                        | \UW\\CODE\VERILOG\COMPARITOR0\Comparitor0.syn]                    | <u> </u>  |

|---------------------------------------------------------|-------------------------------------------------------------------|-----------|

| <u>File View Source Process Options</u>                 | : <u>T</u> ools <u>Wi</u> ndow <u>H</u> elp                       |           |

| 🗍 🗅 😅 🖬   Normal                                        | 👻 🥙 🚣 🔐 170 CFD 🔲 📪 📴 🦉 🛠                                         |           |

| Sources in Project:                                     | Processes for current source:                                     |           |

| Comparitor0                                             | Link Design                                                       |           |

| GAL 16V8D-15LP                                          | <ul> <li>Linked Equations</li> <li>Fit Design</li> </ul>          |           |

| Comparitor (comparitor0.v)                              | Pre-Fit Equations                                                 |           |

| Verilog Variables                                       | Post-Fit Equations                                                |           |

|                                                         | ✓ ☐ Fitter Report                                                 |           |

|                                                         | ✔ isignal Cross Reference Create Fuse Map                         |           |

|                                                         | Cleate Fuse Map ✓ Chip Report                                     |           |

|                                                         |                                                                   |           |

|                                                         | Verilog Post-Route Simulation Model                               |           |

|                                                         | VHDL Post-Route Simulation Model                                  |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

|                                                         |                                                                   |           |

| ×                                                       |                                                                   |           |

|                                                         |                                                                   |           |

| FUSEASM Fusemap Assembler<br>ispLEVER 5.0 Copyright(C), | 1992-2005, Lattice Semiconductor Corporation. All rights reserved |           |

| Portions Copyright(c), 199                              | 2-1999, Vantis Corporation<br>3-1998, Data I/O Corporation        |           |

| Portions Copyright(C), 199                              | 7-1998, MINC Washington Corporation                               |           |

| Portions Copyright(C), Ala<br>Note 5144: Could not open | n Phillips, Lancaster University Computer Centre 1992-1998        |           |

| -                                                       | •                                                                 |           |

| Done: completed successful                              | ly.                                                               |           |

| Automake Log                                            |                                                                   |           |

| 🗐 🕲 🎽 🎆 Clo 💽 Cal 🧭 Eu                                  | . 🕼 My 🔄 D: 🐻 Usi 🌐 isp 🕲 Usi 🏩 Ve 📾 lab 😸 🌾 🏵 🕻                  | V 创 🖵 🛃 🌔 |

Figure 4

# Chip Report – very handy!

- 1. Double-click Chip Report in the Processes for Current Source window.

- 2. Open the Report Viewer window (which should now be displaying the Chip Report).

- 3. Scroll down and you'll see the equations that were created for your design as in Figure 11

| le <u>V</u> iew <u>S</u> ource <u>P</u> rocess <u>O</u> ptions                                                                                                      | <u>T</u> ools <u>W</u> indow <u>H</u> elp                                                         |                      |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|---------------|

| 🗅 😅 🖬 🛛 Normal                                                                                                                                                      | ▼ ♦ ▲ 🔐 10 00 🔲 🗰 🙀 💆 ? №                                                                         |                      |               |

| Sources in Project:                                                                                                                                                 | Processes for current source:                                                                     |                      |               |

| Comparitor0                                                                                                                                                         | ✓C Link Design                                                                                    |                      |               |

| Documents                                                                                                                                                           |                                                                                                   |                      |               |

| GAL16V8D-15LP<br>Comparitor (comparitor0.v)                                                                                                                         | Fit Design                                                                                        |                      |               |

| Verilog Variables                                                                                                                                                   |                                                                                                   |                      |               |

|                                                                                                                                                                     | ✓ Fitter Report                                                                                   |                      |               |

|                                                                                                                                                                     | Jignal Cross Reference                                                                            |                      |               |

|                                                                                                                                                                     | Create Fuse Map                                                                                   |                      |               |

|                                                                                                                                                                     | ✓ ☐ Chip Report                                                                                   |                      |               |

|                                                                                                                                                                     |                                                                                                   |                      |               |

|                                                                                                                                                                     | <ul> <li>Verilog Post-Route Simulation Model</li> <li>VHDL Post-Route Simulation Model</li> </ul> |                      |               |

|                                                                                                                                                                     | VIDE FOSC-Route Simulator Moder                                                                   |                      |               |

| Output files:                                                                                                                                                       | ]                                                                                                 |                      |               |

| Report file :<br>Programmer load file :                                                                                                                             | comparitor0.rpt<br>comparitor0.jed                                                                |                      |               |

| Programmer load file :<br>                                                                                                                                          | comparitor0.rpt<br>comparitor0.jed<br>                                                            | Page 2<br>Thu Sep 08 | 19:00:02 2005 |

| Programmer load file :<br>                                                                                                                                          | comparitorO.jed<br>tarter - Device Utilization Chart                                              |                      | 19:00:02 2005 |

| Programmer load file :<br>ispLEVER 5.0.01.73.31.05_S<br>P16V8AS Programmed Logic:<br>greater = ( a & !c<br># a & b &<br># b & !c.                                   | comparitorO.jed<br>tarter - Device Utilization Chart                                              | Thủ Sep 08           | 19:00:02 2005 |

| Programmer load file :<br>ispLEVER 5.0.01.73.31.05_S<br>P16V8AS Programmed Logic:<br>greater = ( a & lc<br># a & b &<br># b & lc<br>I<br>ispLEVER 5.0.01.73.31.05_S | comparitorO.jed<br>tarter - Device Utilization Chart<br>                                          | Thủ Sep 08           |               |

| Programmer load file :<br>ispLEVER 5.0.01.73.31.05_S<br>P16V8AS Programmed Logic:<br>greater = ( a & !c<br># a & b &<br># b & !c.                                   | comparitorO.jed<br>tarter - Device Utilization Chart<br>                                          | Thủ Sep 08           |               |

| Programmer load file :<br>ispLEVER 5.0.01.73.31.05_S<br>P16V8AS Programmed Logic:<br>greater = ( a & !c<br># a & b &<br># b & !c<br>I<br>ispLEVER 5.0.01.73.31.05_S | comparitorO.jed<br>tarter - Device Utilization Chart<br>                                          | Thủ Sep 08           |               |

| Programmer load file :<br>ispLEVER 5.0.01.73.31.05_S<br>P16V8AS Programmed Logic:<br>greater = ( a & lc<br># a & b &<br># b & lc<br>I<br>ispLEVER 5.0.01.73.31.05_S | comparitorO.jed<br>tarter - Device Utilization Chart<br>                                          | Thủ Sep 08           |               |

Figure 11

Scroll down further and you'll see a visual layout of the pin assignments (Figure 12)....which is very handy for wiring! 3.

Figure 12