-

Notifications

You must be signed in to change notification settings - Fork 7

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

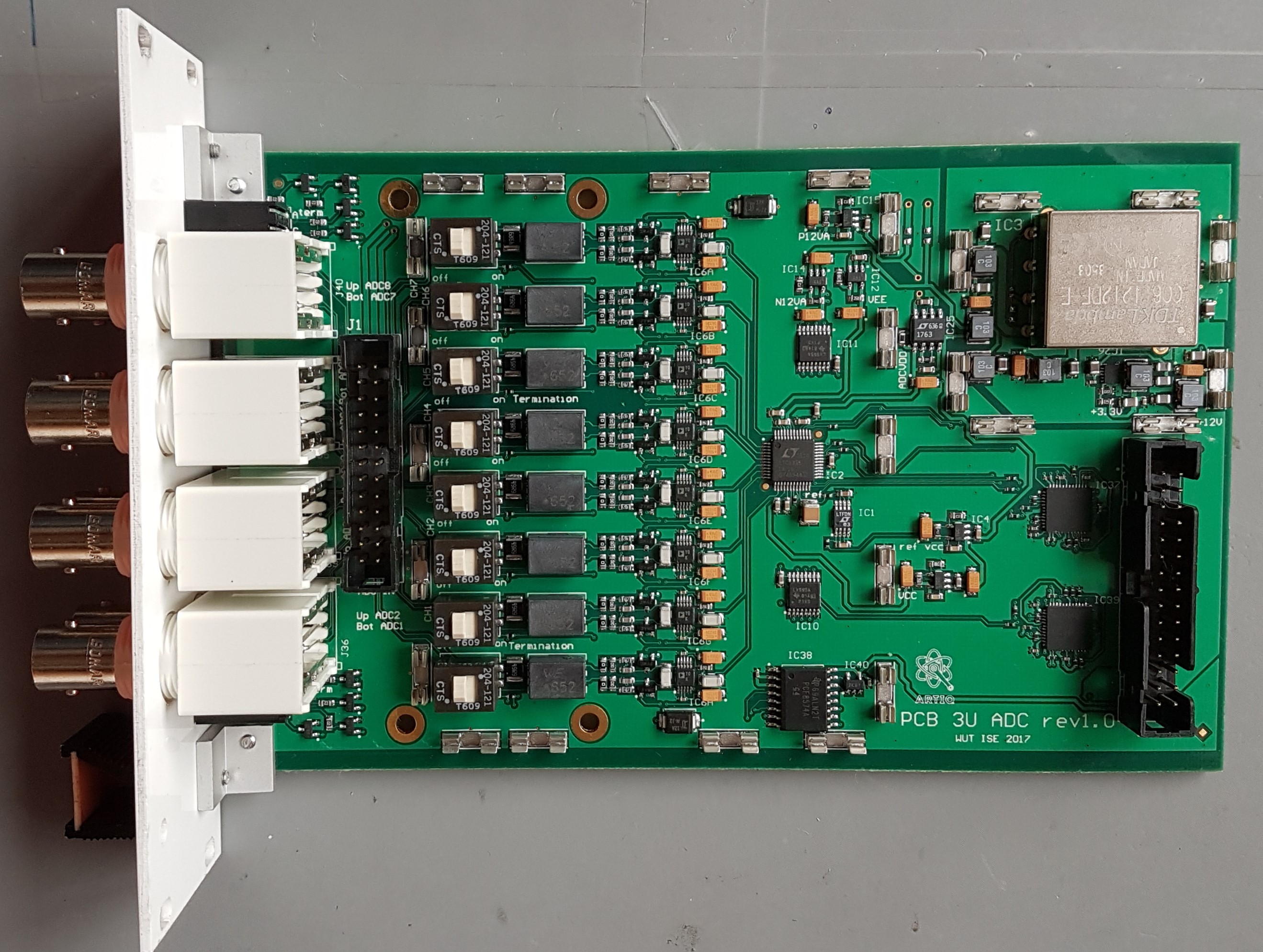

3U ADC (Novo) tests & rev1 errata #226

Comments

|

@gkasprow What tests do you plan to do on this board? If we're going to make a new version with a different ADC, I don't think we need to test this version too carefully. |

|

Sounds like a good plan, thanks Greg! |

|

Today I powered it on. The DC/DC converter generates +3/ -2.5V without load (output chokes removed). Will debug it next week. |

|

power supply works. There were two tantalium capacitor with wrong polarisation. |

|

I managed to communicate with devkit and acquire samples but it works only for DC. |

|

@gkasprow Thanks for the update. What tests do you want to do before you send us some of the ADC/DAC the boards? |

|

(I'm keen to give M-Labs a DAC board asap so that they can write the software for it.) |

|

I'd like to test ADC AC performance to if see if gain change works and do multichannel tests at high SPI rate. |

|

In the absence of Kasli, and metlino we'll have to develop with the vhdci carrier and fmc-vhdci and kc705. Do we have them or could you send some as well? |

|

Recently batch of fmc-vhdci boards were produced for Joe and shipped to US. There were more boards produced and are kept on stock so you can buy them. |

|

@jordens I can send you one of the fmc-vhdci I ordered. What address should I use? |

|

Thanks @jbqubit |

|

I do not have a spare VHDCI_carrier. |

|

Please send the adapter(s) to M-Labs HK, we'll also need them for Zotino. M-Labs Limited |

|

Might be better to send them to QUARTIQ. |

|

I have one spare VHDCI carrier.

|

|

Thanks @gkasprow. NB this has a slightly different pin-out to the new version, due the the reallocating of cc pins... |

|

@jordens @sbourdeauducq Am I sending qty 1 fmc-vhdci to Hong Kong or Germany? |

|

one to HK. |

|

One unit shipping to HK today. @sbourdeauducq you'll need a VHDCI cable. #234 |

|

Supply works fine. Just reversed caps caused all the problems. DAC died on one of the boards probably due to reverse biasing. Shottky diodes needed at the LDO outputs to prevent such situation. |

|

@jordens For reference, what is mailing address of QUARTIQ? |

|

@gkasprow What's the status of the tests on the ADC/DAC boards? When do you anticipate being ready to ship the prototypes to us/M-Labs? |

|

the boards are on a way to mLabs

… |

|

Great! Can you also ship us a couple of each to test out, please? |

|

Once I test them I will do so. |

|

@jordens @hartytp I removed the CMC . Here is the plot. |

|

From a quick look at the text file, that doesn't look any better... |

|

It's worth simulating pulse response in SPICE |

|

Yes, that sounds like a good idea. |

|

@hartytp I simulated it: |

|

After 10us we have 4.998 at the output and 5.017 at the input |

|

Are you sure there isn't something funny going on with the signal generator you're using for this measurement? |

|

Yikes! Well, at least that clears up some of the mystery... |

|

Good catch @gkasprow. Can you remeasure the step response using a better signal generator, using the RC components on the schematic. If that looks better, we can finish testing of the board. |

|

@gkasprow I added your cross-talk measurements to the Wiki. Thanks for taking that data! |

|

@gkasprow I'd like to finish testing this board asap, so we can move on to other things like the RF PA. If you can do it quickly, please could you remeasure the step response with a faster-settling source. If that's a problem/will take too much time, please ship the boards as they are and we'll do this test ourselves. Either way, let me now what you want to do. |

|

@hartytp I brought yet another DDS generator - it is powerfull Tektronix AWG5002B. And the square wave it generates is not better than previous one. So it does not make sense to do any tests with these. Probably simple TTL gate would give better shape, but I don't have time to experiment with it. |

|

@gkasprow Two suggestions:

Otherwise, ship us the boards, and we will make this measurement. |

|

@dhslichter I measured large signal gain: |

|

@dhslichter do you want me to apply 1.2nF and 51Ohm filter to all channels or leave as it is now? |

|

@gkasprow Great! So the -6dB bandwidth is unchanged for full-scale signals. In that case, the settling-time should be absolutely fine. Let's close testing for this board here. If that works okay, I'm happy to leave the original RC values in this version -- the next revision will have different driver OpAmp and a different ADC, so there is no point carefully testing drive impedances in this revision. |

|

Thanks again for all the hard work on this Greg, I'm really happy with the performance of this board! It's also good to know that this will be okay for Allaki etc. |

|

measurements for 1nF and 51Ohm RC filter: at 1Vpp and G=10 (-7.76dBFS) : 382kHz (-6dB) |

|

@hartytp btw, Allakis are already assembled, will get them tomorrow. |

|

@gkasprow Thanks for the data, good to know that 51R and 1nF works as well. That's not directly comparable to our previous measurements, since it replaces the 250kHz LPF with a 3MHz LPF. This will have the effect of increasing the ADC noise floor a bit. Let's stick with the original RC components for this revision, and rethink them in the next revision. NB however: because of the relatively high ADC drive impedance, the DC accuracy will depend on the ADC sample rate, which is a bit nasty! Definitely something to fix next time around. |

Great! |

|

If anyone wants to measure the settling time properly, there are a bunch of classic app notes describing different approaches. |

Sure, it's not that hard -- particularly since this board only has a couple of hundred kHz BW and is only 16-bit. It can also be done with a couple of transistors and a decent voltage source. Anyway, the data we have is sufficient to show that Novo works to specification, so we can leave further data taking to interested users... |

|

Wiki updated. |

|

@gkasprow no need to do any additional measurements for my benefit. |

Revision 1 errata:

Tests to perform. @gkasprow Feel free to skip any of these tests if they're hard to do/you think they're not worth it!

If easy, check the board's temp co (say, for 0V and max V inputs, for G=1 and G=100). If this will take too long, feel free to skip it as we can trust the data sheets.ADC boards arrived

The text was updated successfully, but these errors were encountered: