Apple II VGA PCB #15

Replies: 9 comments 21 replies

-

|

My PCBs arrived from JLCPCB today (cost worked out to about $5.10 ea for the card and a stub for the rear panel, for 5 boards) and parts had arrived earlier this week, so time to put them together and see if things worked... Two changes I'd make for the next revision: Fix the "1uF" labels to read "0.1uF" as they should, and make the card fingers section maybe 1-2mm narrower (the boards are rather snug in the expansion socket). |

Beta Was this translation helpful? Give feedback.

-

|

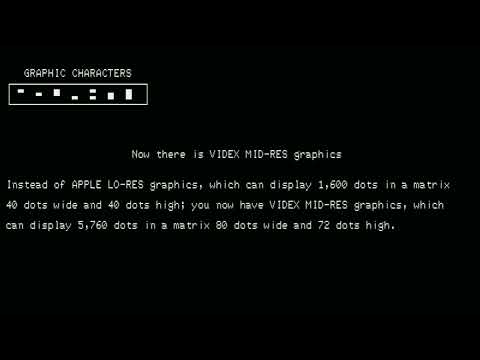

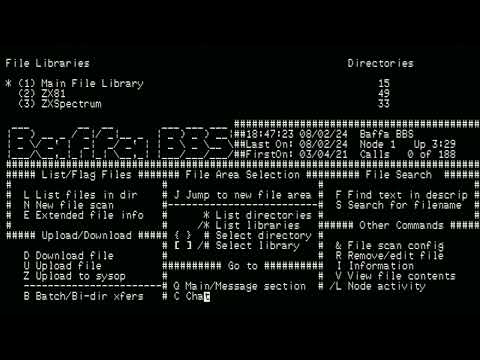

I disabled the read cycle part of abus.c and abus.pio and tried it out in the IIe with very positive results: I'm planning on tidying stuff up and pushing the project to github soon (under some permissive license) and also thinking about doing a version with a TI TFP410 DVI/HDMI encoder as well -- could provide both VGA and HDMI from a single board, I believe. |

Beta Was this translation helpful? Give feedback.

-

|

Nice board, the output looks good. Thanks for sharing! Those are some good trade-offs you made in the design for a more IIe focused board. I originally wanted to add Videx emulation for II+ 80-column support but not much software really used it so ultimately abandoned the idea. Without that there's not a good reason to keep the device read_cycle support. Did I read that right, that you paid ~$26 for 5 PCBs with gold-plated edge connectors? Wow, I would've also taken that deal instead of hand wiring 😀 |

Beta Was this translation helpful? Give feedback.

-

|

I'm interested in playing with the read cycle stuff to maybe implement some kind of IO, network, or disk interface, though I think I'd probably want /IOSEL as well as /DEVSEL for that, so a slightly different board might be called for. JLCPCB is rather impressively inexpensive and fast -- $23.50 for 5 of the main PCBs and $2 for 5 of the little VGA connector + header board (HASL not ENIG for those) for the rear panel. $17 for shipping. Six days from placing the order to boards arriving by DHL. I love the "use multiple buffers to sample chunks of the bus in sequence" approach to conserving GPIOs and I am absolutely going to steal the idea for a ZX81 IO interface project to simplify things there -- there's a little less headroom at 3.5MHz, but I think it should still be workable (and I probably only need two buffers of capture, worst case, for that one). I also changed the power setup slightly -- using the 3V3 out from the Pico to power the buffers and supplying 5V to the Pico's VSYS from the Apple II bus, using a P-FET to disable this if VBUS is present (per the suggestion in section 4.5 of the Pico datasheet). |

Beta Was this translation helpful? Give feedback.

-

|

I pushed everything to github here: https://github.com/swetland/appleii.vga |

Beta Was this translation helpful? Give feedback.

-

|

Looking at disassembly of abus_loop(), it seems like the compiler is inlining a lot of stuff and generating a fair bit of code. When I was poking at my ZX81 IO project I wasn't even using the PIO, just having core1 implement the Z80 bus interface in a tight loop written in thumb assembly (this was easier because I wasn't running anything as intensive as VGA on core0), figuring I'd further optimize using the PIO later. The approach I took for reading was having a small array of register values so when a read happened the only work to do was use the low address bits to index into this array, push the value out to the Z80 bus, and flip a bit in a status register (which would be reset by core0 code later) so the Z80 could tell if it was reading things too quickly. I think a similar approach may work here -- probably easier for custom new peripherals than for emulating existing hardware that may have more work that must be done between back-to-back bus operations than cycles available -- but the general model is to try to have the registers always ready to read so you don't have to call out to any other code during the read cycle. It might not even require writing it in assembly... possibly something like this might be workable: volatile uint8_t abus_card_register[16];

void __time_critical_func(abus_loop)() {

while(1) {

uint32_t value = pio_sm_get_blocking(CONFIG_ABUS_PIO, ABUS_MAIN_SM);

uint32_t address = (value >> 10) & 0xffff;

bool is_write = ((value & (1u << (CONFIG_PIN_APPLEBUS_RW - CONFIG_PIN_APPLEBUS_DATA_BASE))) == 0);

if(((value & (1u << (CONFIG_PIN_APPLEBUS_DEVSEL - CONFIG_PIN_APPLEBUS_DATA_BASE))) == 0)) {

if (!is_write) {

// device read access

pio_sm_put_blocking(CONFIG_ABUS_PIO, ABUS_DEVICE_READ_SM, abus_card_register[address & 0xf]);

}

// possibly signal that a read occurred, flip a status bit somewhere, etc...

gpio_xor_mask(1u << PICO_DEFAULT_LED_PIN);

}

shadow_memory(is_write, address, value);

}

}I'm stuffing another board so I can use one for a display and a second as an experimental peripheral and try this out and see what there is to see. |

Beta Was this translation helpful? Give feedback.

-

|

An excessively debug-instrumented Apple II VGA board (SWD debug probe, Serial to USB adapter, and big red physical reset button just in case): We'll see if I can get away without stuffing the headers for connecting an oscilloscope or logic analyzer to the Apple BUS or not... |

Beta Was this translation helpful? Give feedback.

-

|

So once you get this going, you might want to consider dropping the Pico board and going directly to an RP2040...you will get your extra GPIOs and can use 3 of them to add one more bit of color to each RGB. Thinking ahead for the iigs version. |

Beta Was this translation helpful? Give feedback.

-

|

Quick question on timing, @markadev -- I notice you figure an 18ns buffer plus clock input delay for rising PHI0 and 28ns for falling. Are those based on measured or estimated times from the '07, and/or do they factor in some data on general RP2040 input delays? While tinkering with the PIO programs to handle IOSEL as well as DEVSEL (I've now got a readable "rom" at 0xCn00 as well as the register bank) I noticed this and realized that the tPHL/tPLH on the 74LVC245As (which I'm using for the clock) are not asymmetrical and also faster (2.9ns typ, 6.3ns max), so I may want to slightly tweak these for my board. I probably should just put a scope on it and see exactly what's going on, but I'm still curious for the basis of your timing computations. Thanks! The experimental scanline effect looks nice. I wired up /DEVSEL 0xF as a toggle so I could flip it on and off from the IIe itself, but I'm thinking I'll probably end up leaving them on. |

Beta Was this translation helpful? Give feedback.

-

I recently bought an Apple IIe on ebay and was thinking "maybe you could do a video card by just snooping bus writes"... a bit of searching trying to figure out if that was feasible landed me here where I got my answer along with "and it's already been done."

I thought it'd be fun to build one and I'm not fond of working with perfboard so I fired up KiCAD and ended up with this...

I kept the design very close to the original, so I could try the firmware with minimal changes. I used four buffers for all the bus signals to reduce the number of IC types needed, and the board can be configured to make D0..D7 input only and route SYNC to the Pico instead of direction control for D0..D7 as an option to explore trying to synchronize video updates.

Beta Was this translation helpful? Give feedback.

All reactions