-

Notifications

You must be signed in to change notification settings - Fork 63

Home

Stanislav Zhelnio edited this page Jul 3, 2019

·

12 revisions

A small MIPS CPU core originally based on Sarah L. Harris MIPS CPU ("Digital Design and Computer Arhitecture" by David Money Harris and Sarah L Harris). The first version of schoolMIPS was written for Young Russian Chip Architects summer school.

The schoolMIPS have several versions (from simple to complex). Each of them is placed in the separate git branch:

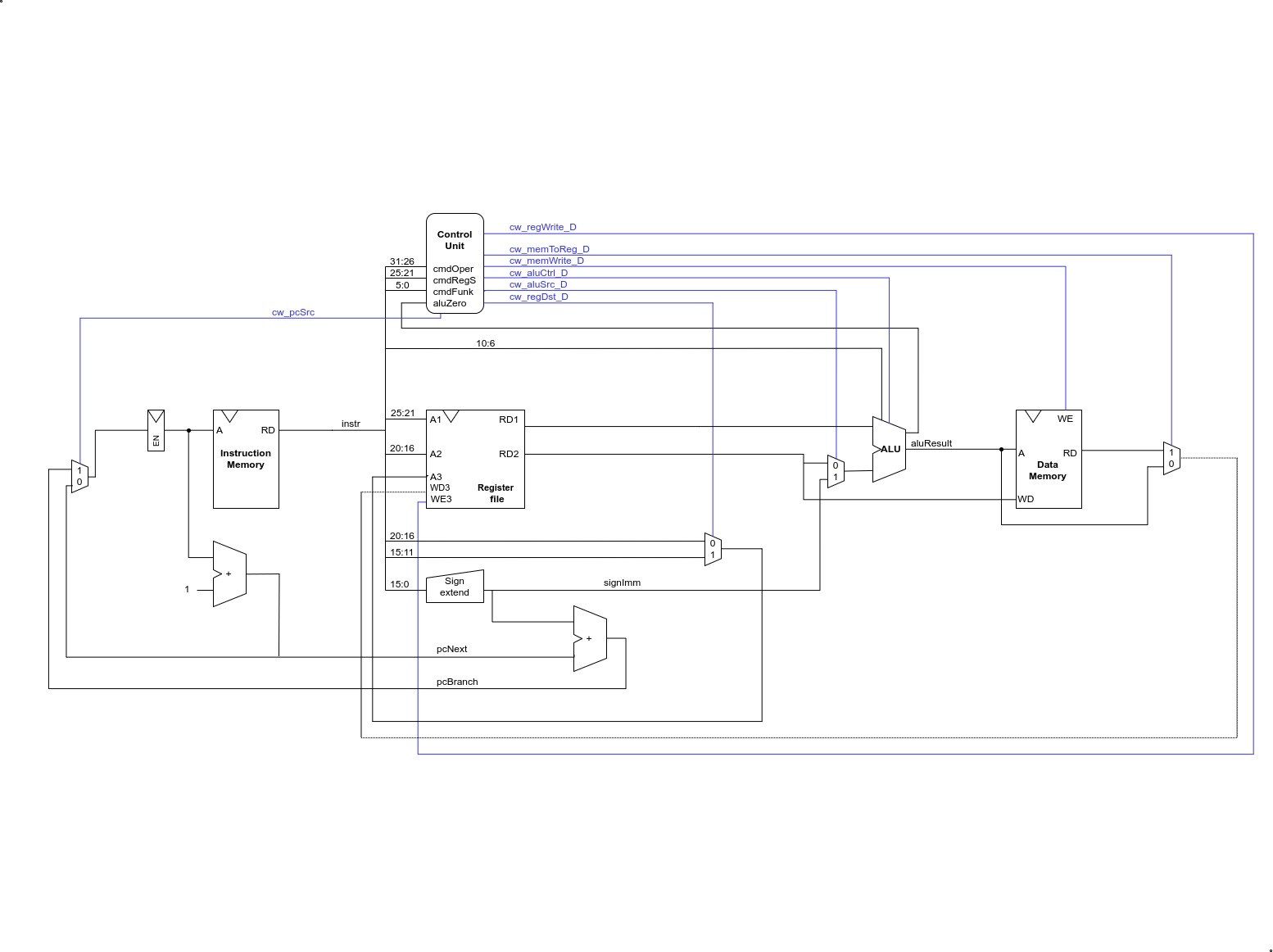

- 00_simple - the simplest CPU without data memory, but the programs for this core are compiled using GNU gcc;

- 01_mmio - the same but with data memory, simple system bus and peripherals (pwm, gpio, als);

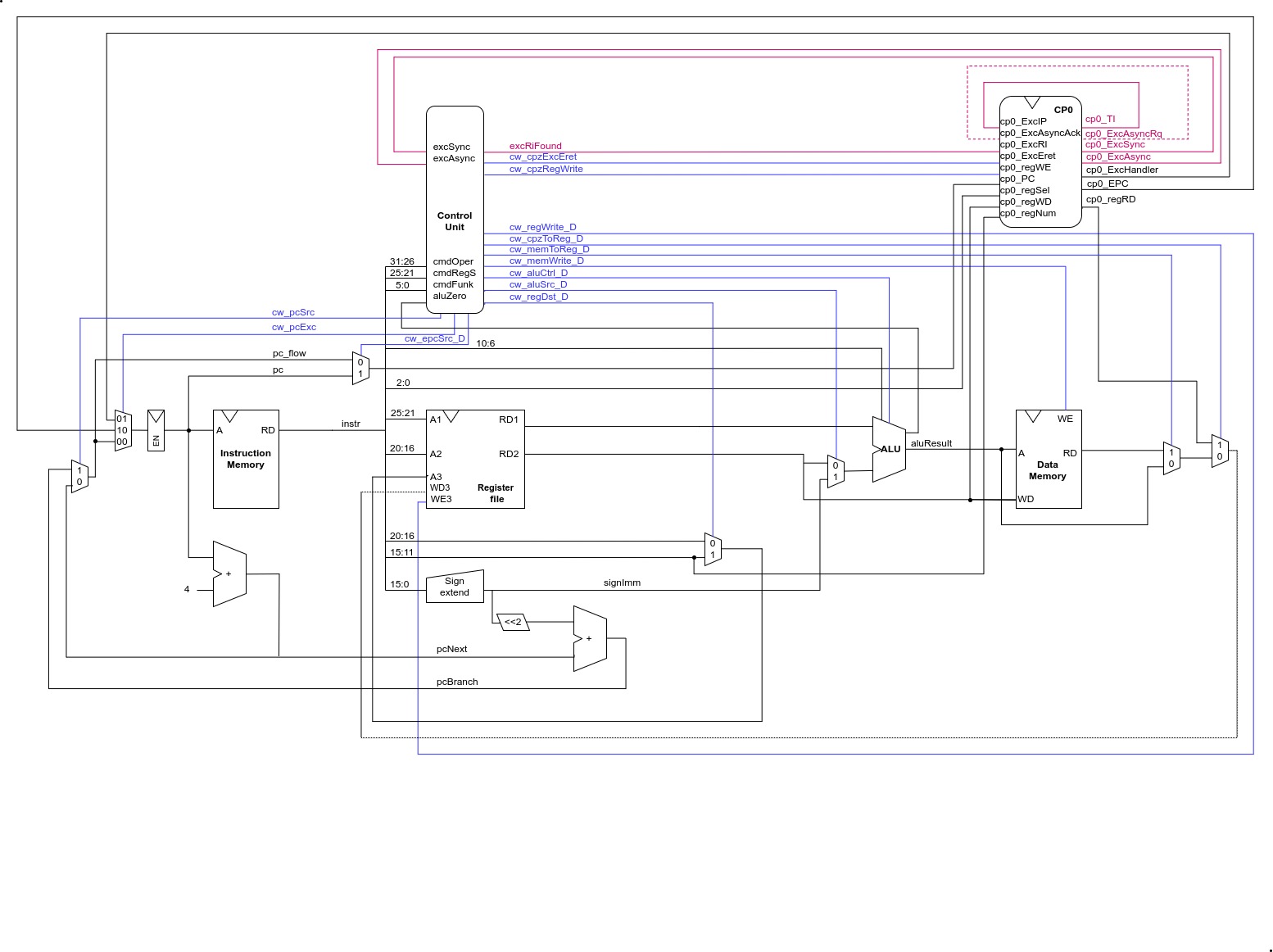

- 02_irq - data memory, system timer, interrupt and exceptions (CP0 coprocessor);

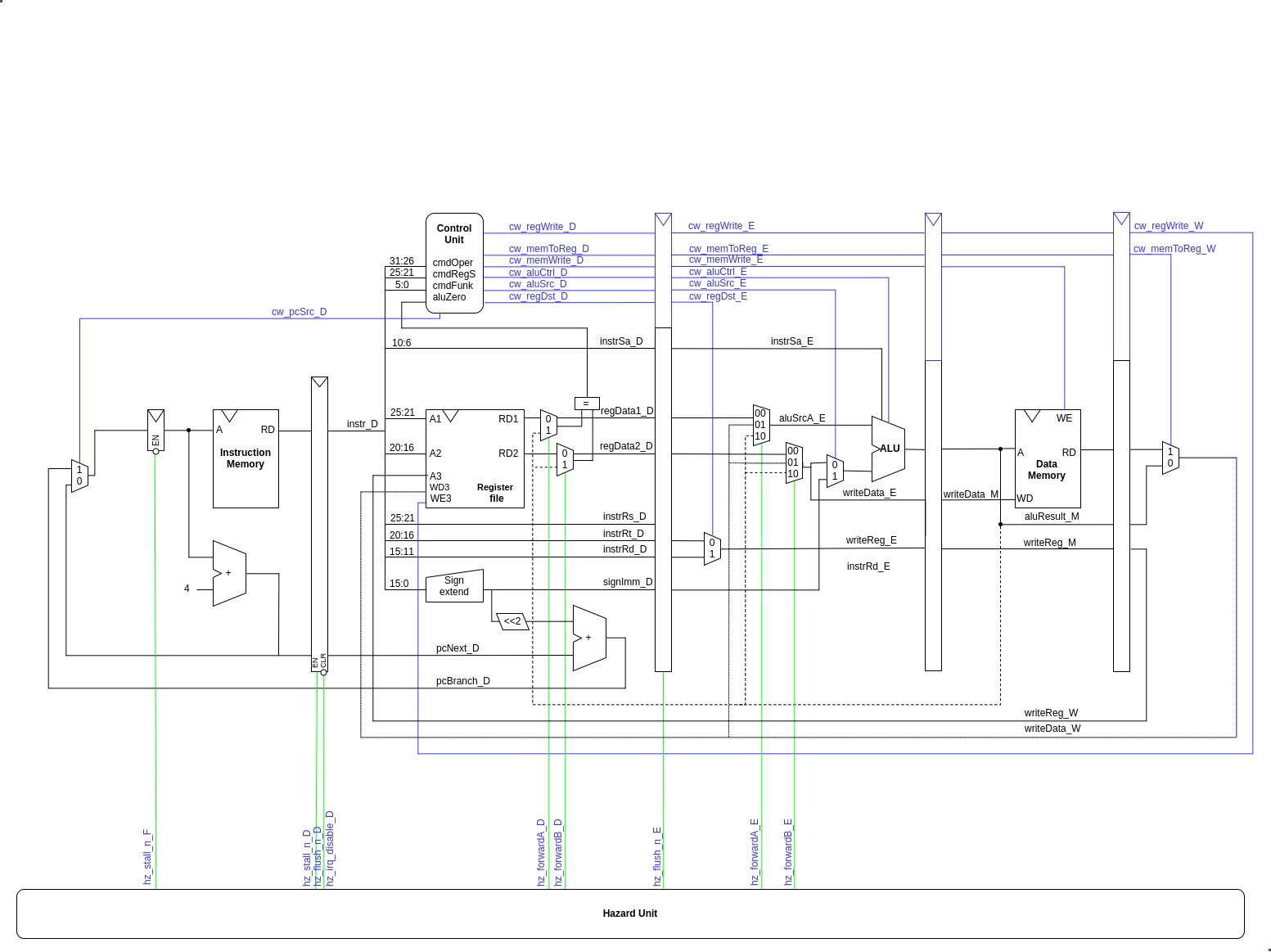

- 03_pipeline - the pipelined version of the simplest core with data memory

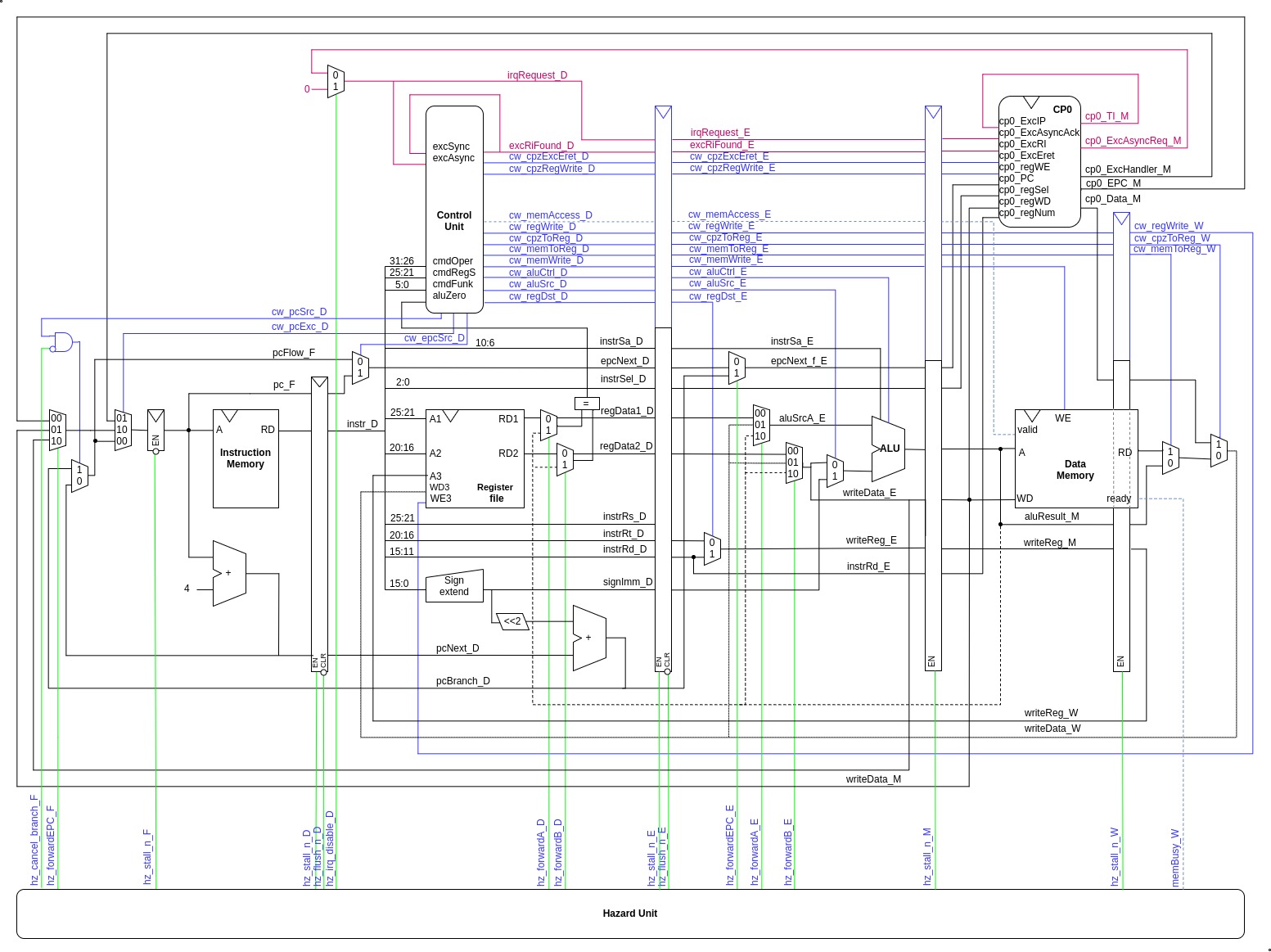

- 04_pipeline_irq - the pipelined version of 02_irq

- 05_pipeline_ahb - 04_pipeline_irq with AHB-Lite bus support and Scratchpad RAM

- schoolMIPS User Manual (Russian)

- schoolMIPS slides for 00_simple (Russian, English)

- Digital Design and Computer Arhitecture (Russian)

- MIPS32 Instruction Set Quick Reference (pdf)

- MIPS Architecture For ProgrammersVolume II-A: The MIPS32 InstructionSet (pdf)

- AHB-Lite slides (English)

Examples of using this kernel as an element of a multiprocessor system:

- A.E. Ryazanova, A.A. Amerikanov, E. V Lezhnev, Development of multiprocessor system-on-chip based on soft processor cores schoolMIPS, J. Phys. Conf. Ser. 1163 (2019) 012026. doi:10.1088/1742-6596/1163/1/012026.

- Innovate FPGA 2019 project: EM028 » NoC-based multiprocessing system prototype

You can use ubuntu-hdl-tools-install project to create an Ubuntu virtual machine with a set of HDL and MIPS development tools:

- Icarus Verilog & GTKWave

- MARS MIPS Simulator

- Intel Quartus Lite 17.1

- Xilinx Vivado SDK 2018.1

- MIPS Toolchain

- Microsoft Visual Studio Code

- Sublime Text 3

- git

- openocd

System bus and peripheral devices are not shown