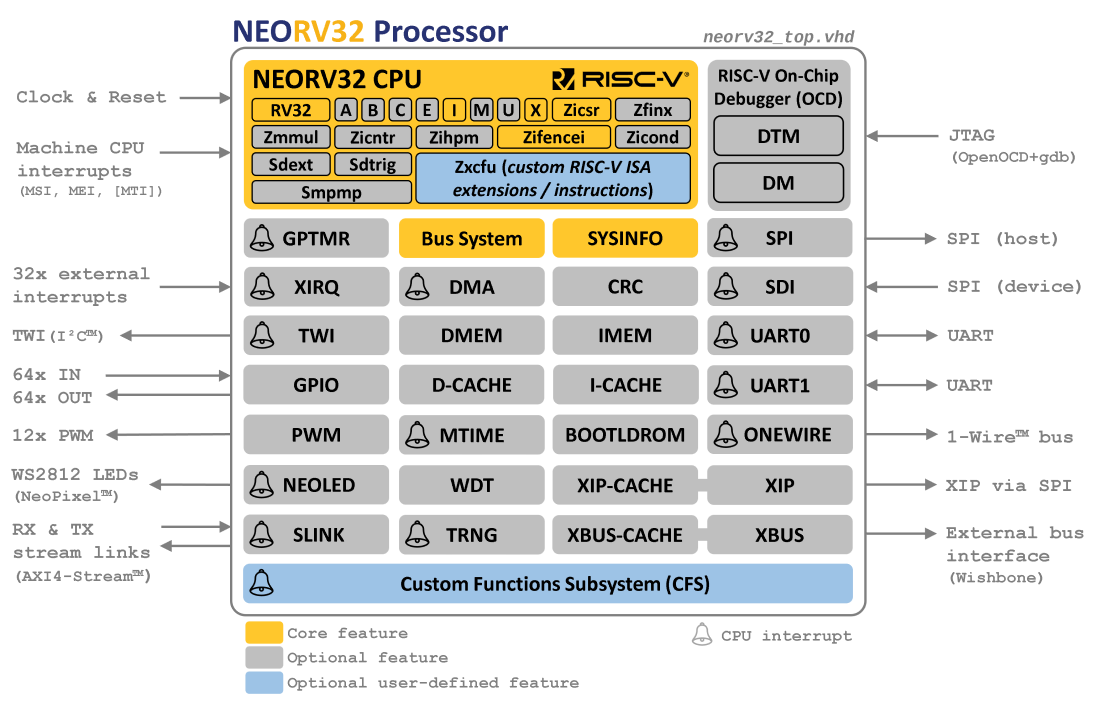

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) built around the NEORV32 RISC-V CPU that is written in platform-independent VHDL. The processor is intended as auxiliary controller in larger SoC designs or as tiny and customized microcontroller that even fits into a Lattice iCE40 UltraPlus low-power & low-density FPGA. The project is intended to work out of the box and targets FPGA / RISC-V beginners as well as advanced users.

Special focus is paid on execution safety to provide defined and predictable behavior at any time. For example, the CPU ensures all memory accesses are properly acknowledged and all invalid/malformed instructions are always detected as such. Whenever an unexpected state occurs the application software is informed via precise and resumable hardware exceptions.

- 📚 For detailed information see the NEORV32 online documentation.

- ♻️ Looking for an all-Verilog version? Have a look at neorv32-verilog.

- ✔️ Continuous integration to check for regressions (including RISC-V ISA compatibility check using RISCOF).

- 📦 Exemplary setups and community projects targeting various FPGA boards and toolchains to get started.

- 🪁 Support for FreeRTOS, Zephyr OS and LiteX SoC Builder Framework.

- 🏷️ The project's change log is available in CHANGELOG.md.

- 🚀 Check out the quick links below and the User Guide to get started setting up your NEORV32 processor!

⁉️ Want to know more? Check out the project's rationale.

💡 Feel free to open a new issue or start a new discussion if you have questions, comments, ideas or if something is not working as expected. See how to contribute.

- all-in-one package: CPU + SoC + Software Framework & Tooling

- completely described in behavioral, platform-independent VHDL - no platform-specific primitives, macros, attributes, etc.; an all-Verilog "version" is also available

- extensive configuration options for adapting the processor to the requirements of the application

- highly extensible hardware - on CPU, processor and system level

- aims to be as small as possible while being as RISC-V-compliant as possible - with a reasonable area-vs-performance trade-off

- FPGA friendly (e.g. all internal memories can be mapped to block RAM - including the CPU's register file)

- optimized for high clock frequencies to ease integration / timing closure

- from zero to "hello world!" - completely open source and documented

- easy to use even for FPGA / RISC-V starters – intended to work out of the box

| Task / Subproject | Repository | CI Status |

|---|---|---|

| GitHub pages (docs) | neorv32 |  |

| Build documentation | neorv32 |  |

| Processor verification | neorv32 |  |

| RISCOF core verification | neorv32-riscof |  |

| FPGA implementations | neorv32-setups |  |

| All-Verilog version | neorv32-verilog |  |

| FreeRTOS port | neorv32-freertos |  |

| Prebuilt GCC toolchains | riscv-gcc-prebuilt |  |

The processor passes the official RISC-V architecture tests to ensure compatibility with the RISC-V ISA specs., which is checked by the

neorv32-riscof repository. It can successfully run any C program

(for example from the sw/example folder) including CoreMark

and FreeRTOS and can be synthesized for any target technology - tested

on Intel, Xilinx and Lattice FPGAs. The conversion into a plain-Verilog netlist module is automatically checked by the

neorv32-verilog repository.

The NEORV32 Processor provides a full-featured microcontroller-like SoC build around the NEORV32 CPU. By using generics the design is highly configurable and allows a flexible customization to tailor the setup according to your needs. Note that all of the following SoC modules are entirely optional.

CPU Core

- 32-bit little-endian RISC-V single-core, pipelined/multi-cycle modified Harvard architecture

- configurable ISA extensions:

RV32[I/E] [M] [A] [C] [B] [U] [X] [Zicsr] [Zicntr] [Zicond] [Zihpm] [Zifencei] [Zfinx] [Zmmul] [Zxcfu] [PMP] [Sdext] [Sdtrig] - compatible to subsets of the RISC-V Unprivileged ISA Specification (pdf) and Privileged Architecture Specification (pdf).

machineanduserprivilege modes- implements all standard RISC-V exceptions and interrupts + 16 fast interrupt request channels as NEORV32-specific extension

- custom functions unit (CFU as

ZxcfuISA extension) for custom RISC-V instructions; - intrinsic libraries for CPU extensions that are not yet supported by GCC

Memories

- processor-internal data and instruction memories (DMEM / IMEM) & caches (iCACHE and dCACHE)

- pre-installed bootloader (BOOTLDROM) with serial user interface; allows booting application code via UART or from external SPI flash

Timers and Counters

- 64-bit machine timer (MTIME), RISC-V spec. compatible

- 32-bit general purpose timer (GPTMR) with capture input

- watchdog timer (WDT)

Input / Output

- standard serial interfaces (UART, SPI (host), SDI (SPI device), TWI/I²C, ONEWIRE/1-Wire)

- general purpose IOs (GPIO) and PWM

- smart LED interface (NEOLED) to directly control NeoPixel(TM) LEDs

SoC Connectivity

- 32-bit external bus interface - Wishbone b4 compatible (WISHBONE); wrappers for AXI4-Lite and Avalon-MM host interfaces

- stream link interface with independent RX and TX channels - AXI4-Stream compatible (SLINK)

- external interrupts controller with up to 32 channels (XIRQ)

Advanced

- true-random number generator (TRNG) based on the neoTRNG

- execute-in-place module (XIP) to execute code right out of a SPI flash

- custom functions subsystem (CFS) for custom tightly-coupled co-processors, accelerators or interfaces

- direct memory access controller (DMA) for CPU-independent data transfers and conversions

- cyclic redundancy check unit (DMA) to test data integrity (CRC8/16/32)

Debugging

- on-chip debugger (OCD) accessible via standard JTAG interface

- compatible to the "Minimal RISC-V Debug Specification Version 1.0"

- compatible with OpenOCD, GDB and Segger Embedded Studio

- RISC-V trigger module for hardware-assisted breakpoints

Implementation results for exemplary CPU configurations generated for an Intel Cyclone IV EP4CE22F17C6 FPGA

using Intel Quartus Prime Lite 21.1 (no timing constrains, balanced optimization, f_max from Slow 1200mV 0C Model).

| CPU Configuration (version 1.7.8.5) | LEs | FFs | Memory bits | DSPs | f_max |

|---|---|---|---|---|---|

rv32i_Zicsr |

1223 | 607 | 1024 | 0 | 130 MHz |

rv32i_Zicsr_Zicntr |

1578 | 773 | 1024 | 0 | 130 MHz |

rv32imc_Zicsr_Zicntr |

2338 | 992 | 1024 | 0 | 130 MHz |

💡 An incremental list of CPU extensions and processor modules can be found in the Data Sheet: FPGA Implementation Results.

The NEORV32 CPU is based on a two-stages pipelined/multi-cycle architecture (fetch and execute). The following table shows the performance results (scores and average CPI) for exemplary CPU configurations (no caches) executing 2000 iterations of the CoreMark CPU benchmark (using plain GCC10 rv32i built-in libraries only!).

| CPU Configuration (version 1.5.7.10) | CoreMark Score |

|---|---|

small (rv32i_Zicsr_Zifencei) |

33.89 |

medium (rv32imc_Zicsr_Zifencei) |

62.50 |

performance (rv32imc_Zicsr_Zifencei + perf. options) |

95.23 |

💡 More information regarding the CPU performance can be found in the Data Sheet: CPU Performance. The CPU & SoC provide further "tuning" options to optimize the design for maximum performance, maximum clock speed, minimal area or minimal power consumption: User Guide: Application-Specific Processor Configuration

This overview provides some quick links to the most important sections of the online Data Sheet and the online User Guide.

- NEORV32 Project - introduction

- Rationale - why? how come? what for?

- Key Features - what makes it special

- Structure - folders, RTL files and compile order

- Metrics - FPGA implementation and performance evaluation

-

NEORV32 Processor - the SoC

- Top Entity - Signals - how to connect to the processor

- Top Entity - Generics - processor/CPU configuration options

- Address Space - memory layout and boot configurations

- SoC Modules - IO/peripheral modules and memories

- On-Chip Debugger - in-system debugging of the processor via JTAG

-

NEORV32 CPU - the Core

- RISC-V Compatibility - what is compatible to the specs and what is not

- Architecture - a look under the hood

- Full Virtualization - execution safety

- ISA and Extensions - available (RISC-V) ISA extensions

- CSRs - control and status registers

- Traps - interrupts and exceptions

- Example Programs - examples how to use the processor's IO/peripheral modules

- Core Libraries - high-level functions for accessing the processor's peripherals

- Software Framework Documentation - doxygen-based

- Application Makefile - turning your application into an executable

- Bootloader - the build-in NEORV32 bootloader

- Toolchain Setup - install and setup the RISC-V GCC toolchain

- General Hardware Setup - setup a new NEORV32 FPGA project

- General Software Setup - configure the software framework

- Application Compilation - compile an application using

make - Upload via Bootloader - upload and execute executables

- Application-Specific Processor Configuration - tailor the processor to your needs

- Adding Custom Hardware Modules - add your custom hardware

- Debugging via the On-Chip Debugger - step through code online and in-system

- Simulation - simulate the whole SoC

- LiteX Integration - build a SoC using NEORV32 + LiteX

- Convert to Verilog - turn the NEORV32 into an all-Verilog design

- Overview - license, disclaimer, limitation of liability for external links, proprietary notice, etc.

- Citing - citing information

This is an open-source project that is free of charge. Use this project in any way you like (as long as it complies to the permissive license). Please cite it appropriately. 👍

❤️ A big shout-out to the community and all the contributors! This project would not be where it is without them.