-

Notifications

You must be signed in to change notification settings - Fork 3

IceStudio Exportación a Verilog

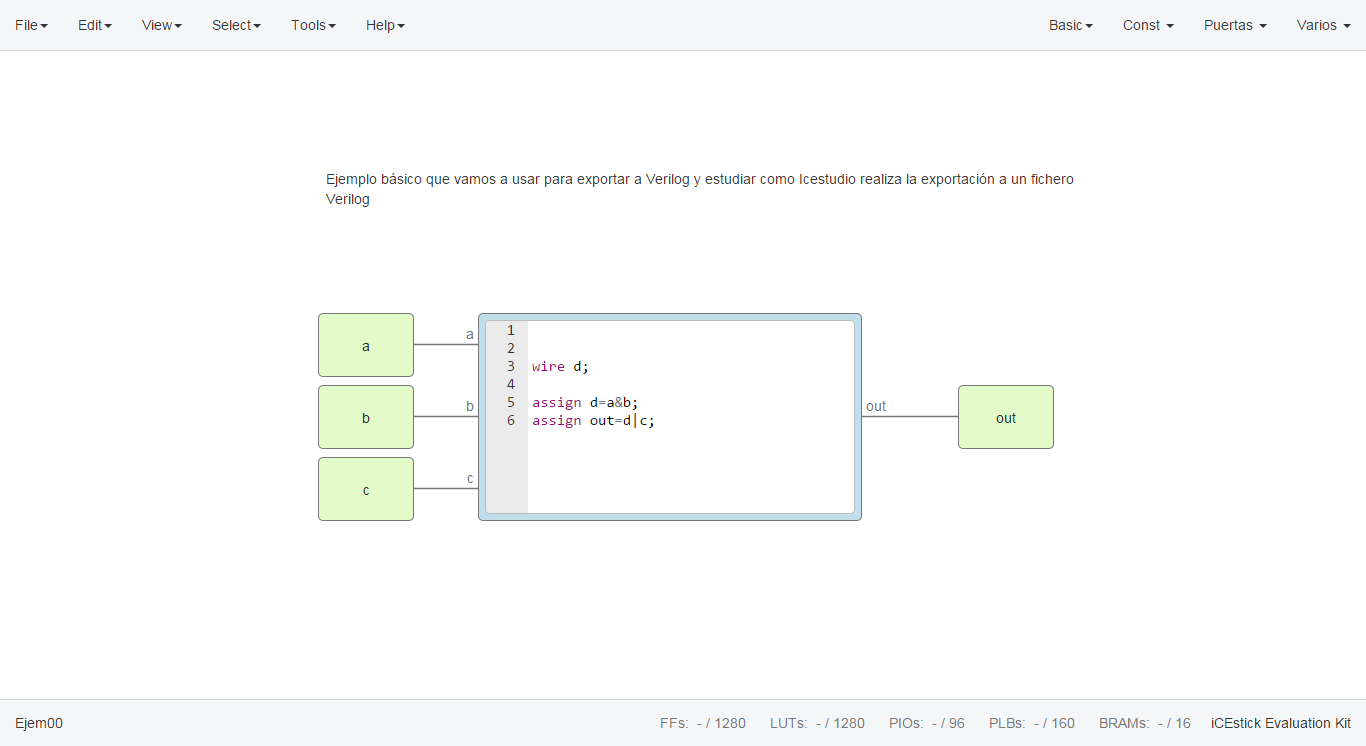

En este apartado vamos a intentar ver como IceStudio realiza la exportación de un fichero *.ice a código Verilog *.v, para ello, vamos a empezar por un pequeño ejemplo en IceStudio donde solo tenemos un bloque de código que equivaldría a un módulo de verilog.

El ejemplo es el siguiente:

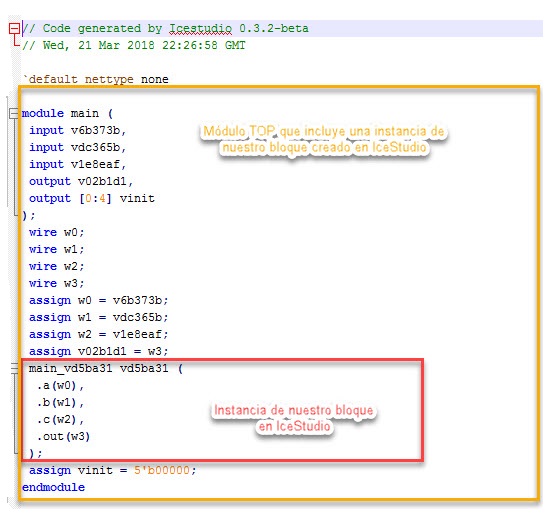

Si abrimos el fichero exportado a Verilog, tenemos:

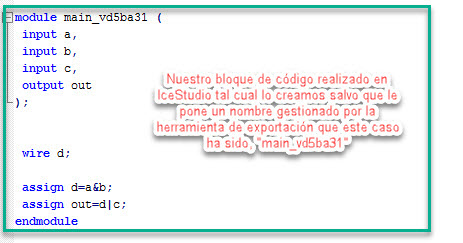

En el fichero Verilog extorpado podemos ver que automáticamente se ha crea un modulo superior (main) que engloba nuestro módulo realizado como bloque de código en IceStudio. Para crear el módulo "main" se crean tantas entradas/salidas como necesite así como un registro de 5 bits ( vinit )que en principio lo veo innecesario. Las entradas/salidas que genera las empareja con las entradas/salidas de nuestro bloque IceStudio creado. Si quisieramos, podríamos borrar todo el modulo "main", renombrar nuestro módulo de IceStudio ("main_vd5ba31") con otro nombre como por ejemplo "ejem00", de esta forma podríamos dejarnos una exportación más limpia/clara aunque el objetivo debe ser usar la herramienta de exportación, comprender como exporta y usar dicha exportación para los fines que se deseen sin tener que tocar nada.

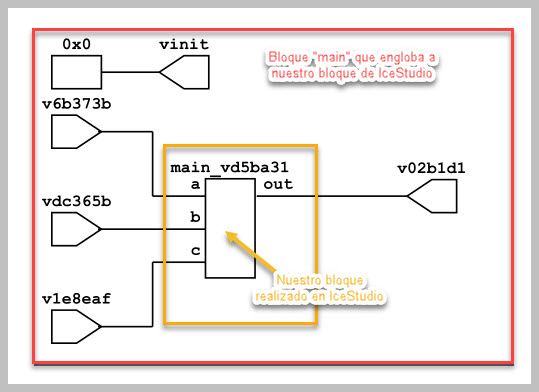

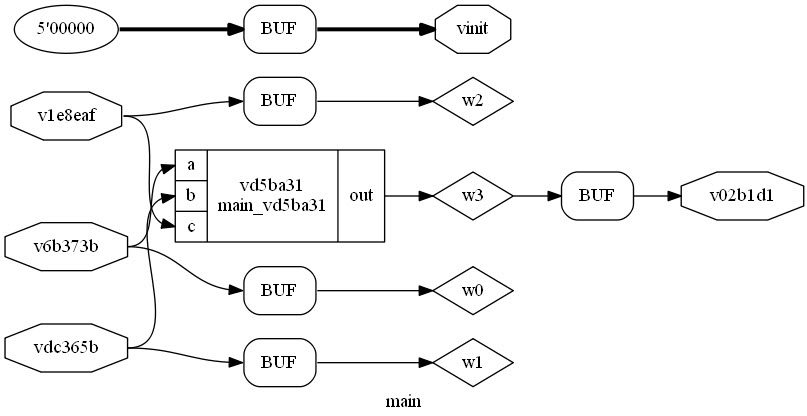

Podemos ver la exportación viendo todo como un módulo "main" que incluye otros "submodulos" que nombrará como "main_xxxx", un esquema gráfico sería:

Aquí podemos apreciar mejor de una forma gráfica las señales de entrada/salida del bloque "main" creadas y el bloque instanciado ( nuestro bloque creado en IceStudio). Sigue sin tener sentido la creación del registro de 5 bits "vinit".

Podemos mostrarlo también con el siguiente dibujo:

Donde también podemos observar un poco más las los nombres de las señales/cables que crea para el módulo principal "main" que contiene nuestro "módulo"realizado en IceStudio.

Una vez visto con un ejemplo sencillo con un único módulo realizado en IceStudio vamos a ver como exporta con un ejemplo de IceStudio que contenga varios módulos ( bloques de código ).

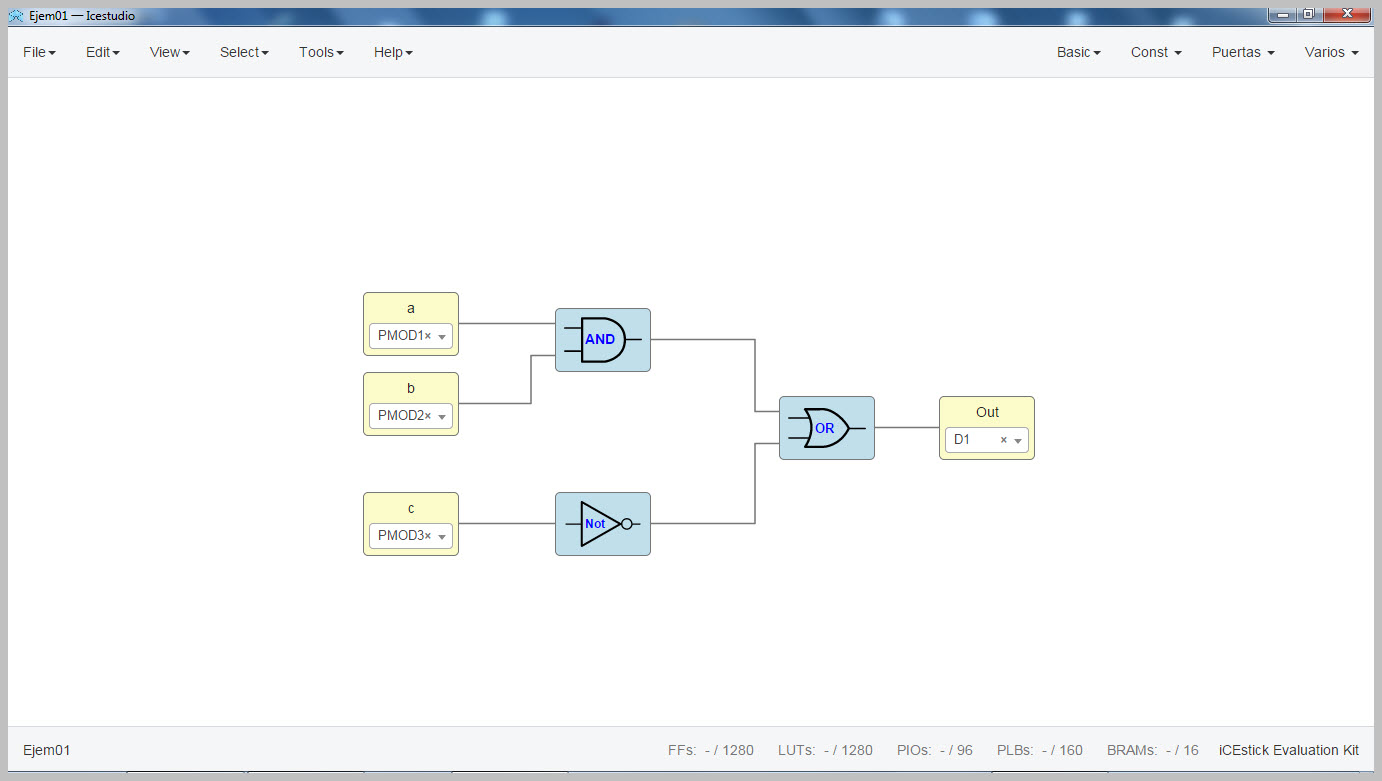

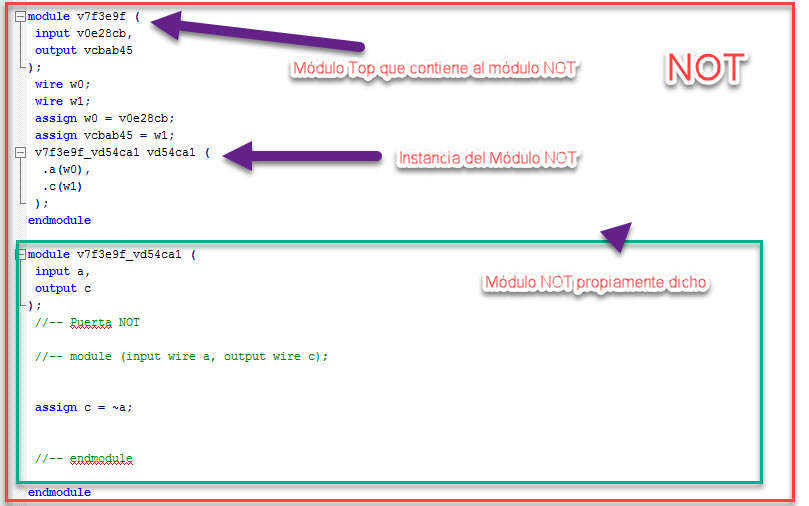

Dado el siguiente ejemplo "Ejem01.ice" realizado en IceStudio:

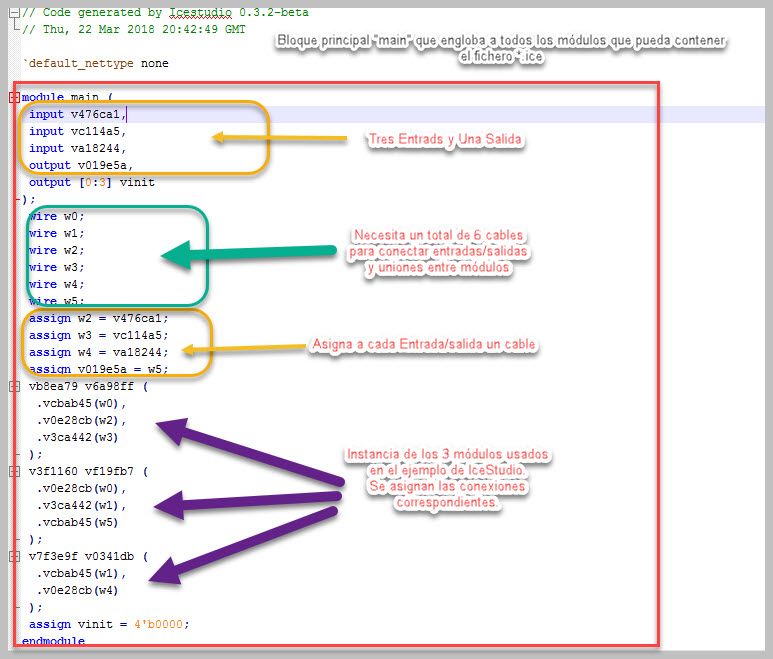

Tras la exportación a Verilog tenemos el siguiente código Verilog:

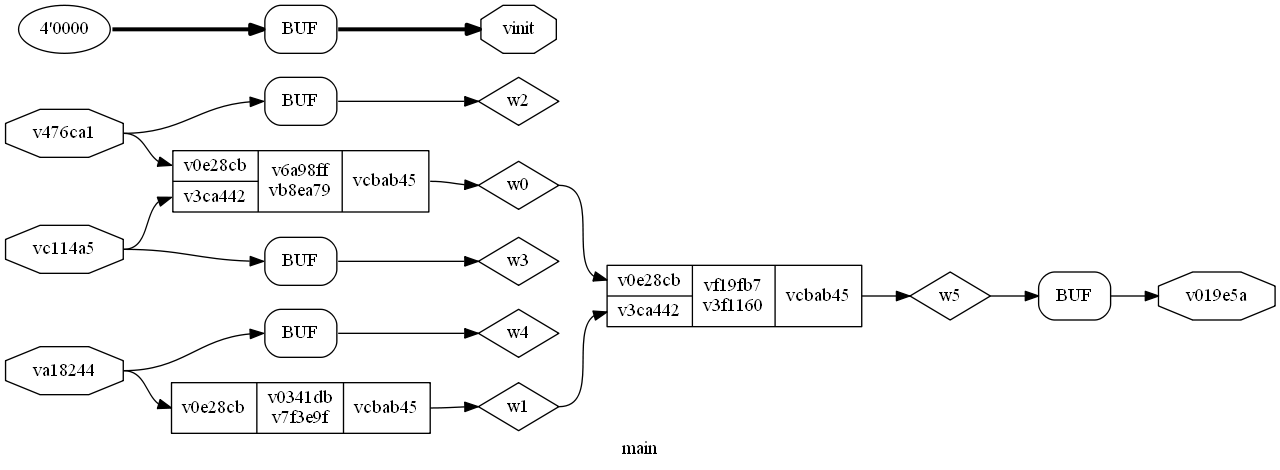

Nos encontramos con un modulo "main" que contendrá tantas señales de entrada/salida como se necesiten para conectar todos los bloques que contenga. Igualmente creará todos los cables necesarios para realizar las interconexiones de todos los bloques y creará las instancias a todos los bloques que contenga asociando los cableados que correspondan.

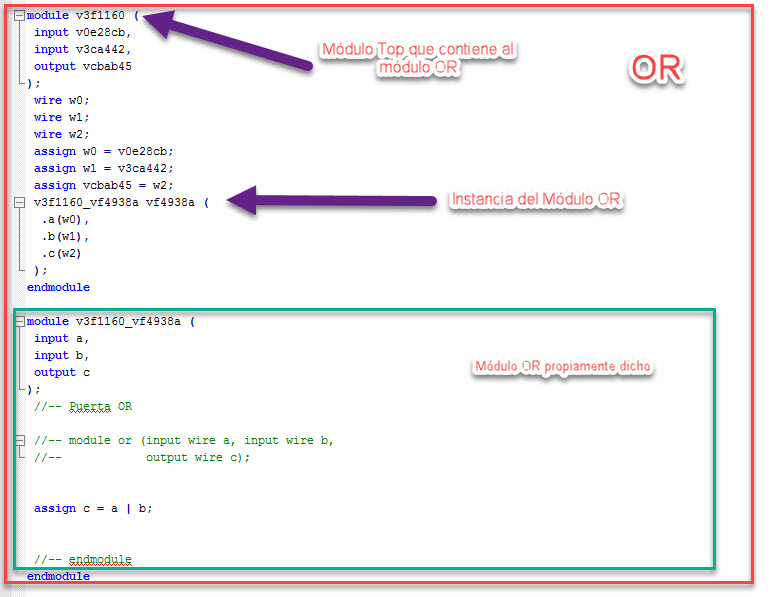

En nuestro ejemplo hay tres bloques ( AND,OR,NOT ) sobre los cuales la exportación ha creado también un módulo TOP que incluye nuestro bloque/módulo (AND,OR,NOT)propiamente dicho.Podemos verlo en las siguientes figuras.

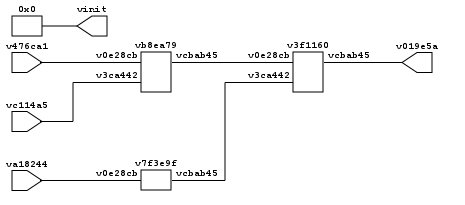

Un esquema de como ha organizado toda la exportación la podemos ver las siguientes dos figuras:

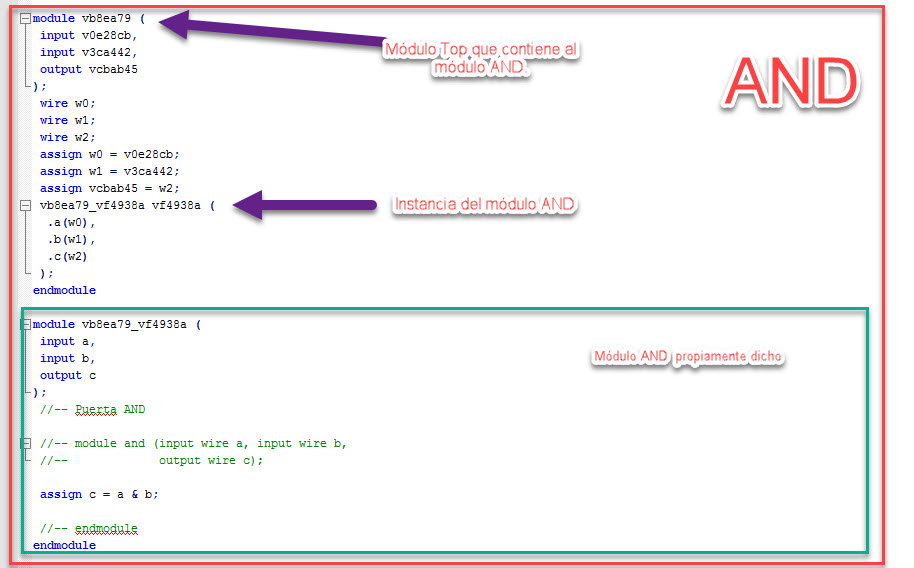

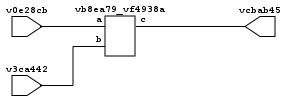

Aquí podemos ver que el módulo "main" contiene tres bloques que están unidos entre ellos por cables ( tipo wire ) y que por ejemplo el bloque AND lo ha llamado "v6a98ff" que es del tipo "vb8ea79" ( Módulo superior del módulo AND propiamente dicho). El bloque AND está formado a su vez por un módulo superior "vb8ea79" que contiene al bloque AND propiamente dicho "vb8ea79_vf4938a" como podemos ver en la siguiente figura:

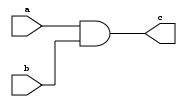

donde "vb8ea79_vf4938a" es un puerta AND simplemente:

Se puede observar el mismo funcionamiento para la puerta OR y la puerta NOT, podemos ver que el proceso de exportación es un tanto laborioso y si el proyecto crece mucho (un bloque formado por muchos sub-bloques) puede ser una tanto laborioso hacer el seguimiento de toda la estructura creada.

Por otra parte, si se entiende, puede ser relativamente fácil llegar a nuestro bloque de inicio (Bottom) que en alguna ocasión puede sernos útil para extraer el fichero verilog de nuestro bloque de una forma más limpia y usarse para otros fines, siendo este extraido desde la herramienta IceStudio.