-

Notifications

You must be signed in to change notification settings - Fork 3

Verilog

Vamos a intentar mostrar el lenguaje de descripción HDL Verilog para poder usarlo en IceStudio así como en cualquier otra plataforma de desarrollo de FPGAs.

A la hora de realizar un proyecto, este se puede descomponer en módulos/partes más sencillas donde la unión de todos los módulos pueden formar un gran proyecto. Igualmente el desarrollo de un módulo nos permitirá la reutilización de hardware en otros proyectos que pueden contener partes similares o iguales.

Un módulo vendrá dado por todo aquello que se encuentra entre las palabras claves module y endmodule.

Un circuito combinacional lógico puede ser descrito desde un esquema de puertas,usando ecuaciones Booleanas o con una tabla de verdad. Verilog puede describir el circuito lógico usando las distintas formas comentadas.

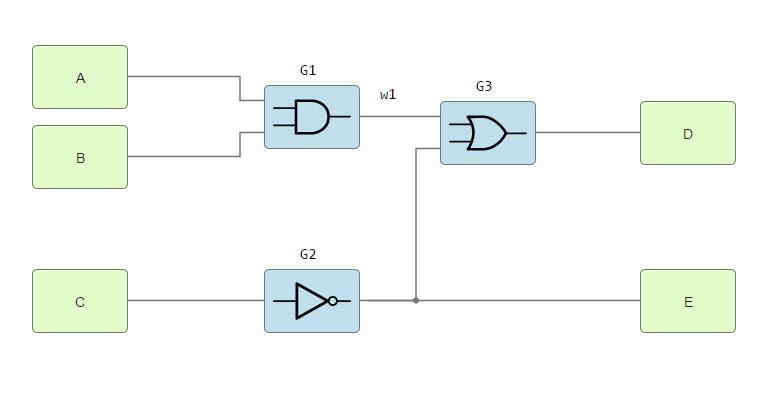

Vamos a ir explicando Verilog con ejemplos. Vamos a crear un módulo donde se describa un esquema lógico como el mostrado en la siguiente figura:

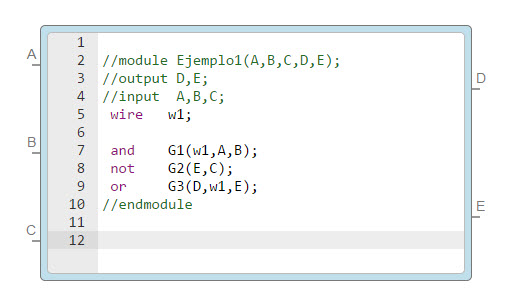

Para describir dicho circuito creamos el siguiente módulo Verilog:

//Después de las barras invertidas se pueden poner comentarios

//que no afectan al código introducido

module Ejemplo1(A,B,C,D,E);

output D,E;

input A,B,C;

wire w1;

and G1(w1,A,B);

not G2(E,C);

or G3(D,w1,E);

endmodule

Podemos ver que el módulo está formado por el nombre que lo define "Ejemplo1" en este caso y por una lista de puertos que este ejemplo está formada por una lista de 5 puertos (A,B,C,D,E). A su vez estos puertos se definen como puertos de salida o de entrada ( D,E como salidas y A,B,C como entradas ), podemos ver que se ha definido un cable "w1" mediante el tipo "wire", esto será equivalente a un cable físico ( el cable w1 será el cable que une la salida de la puerta AND con una de las entradas de la puerta OR ).

Para crear el módulo verilog anteriormente descrito en Icestudio se puede hacer de dos formas:

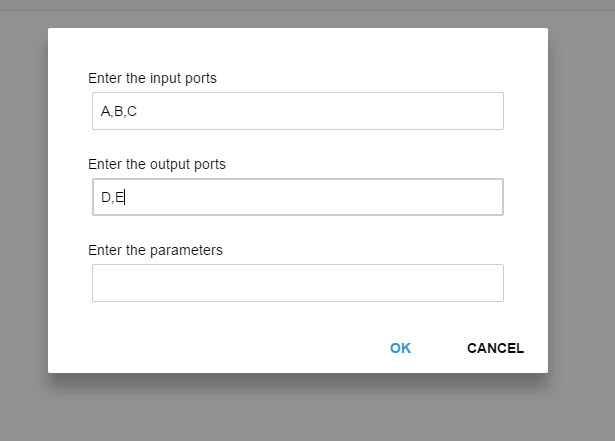

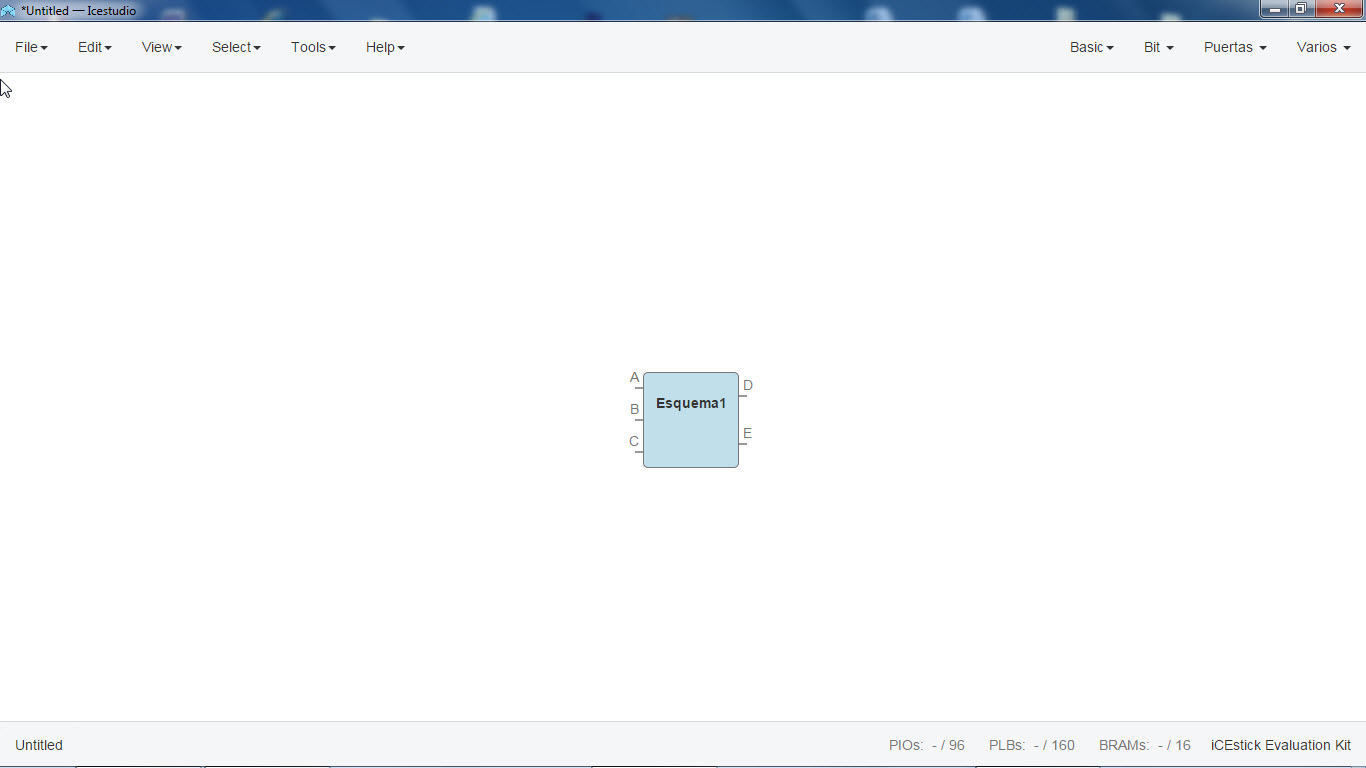

A.Creando una caja de código desde Basic-->Code donde se introducirán los puertos de entrada-salida que tiene el módulo e introduciendo el código tal cual en el módulo descrito ( a excepción de las salidas-entradas ya definidas y de la palabra clave endmodule )

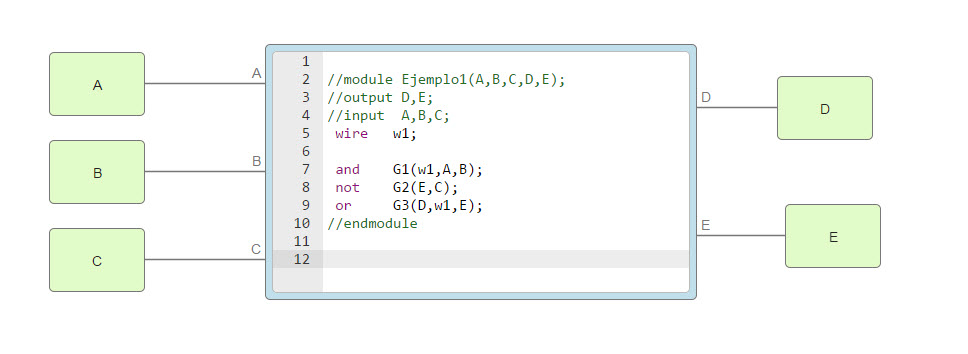

Una vez definidas las entradas-salidas e introducido el código podemos añadir los puertos de entrada-salida desde Basic-->Input / Basic-->Output.

Una vez creado el módulo, se podrá salvar y ser reutilizado introduciendolo como un bloque.

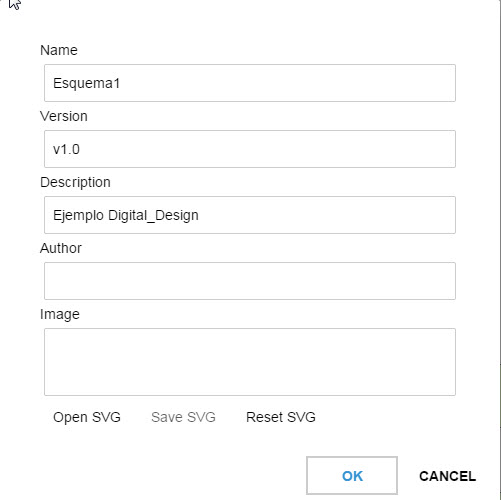

Desde Edit-->Project Information podemos darle un nombre al módulo y crear una pequeña descripción o incluso asignarle una imagen que lo represente mejor.

Una vez guardado el módulo se podrá usar en otro proyecto añadiendo el módulo desde File-->Add as block.

Si hacemos doble click sobre el módulo creado se nos mostrará el código del módulo.

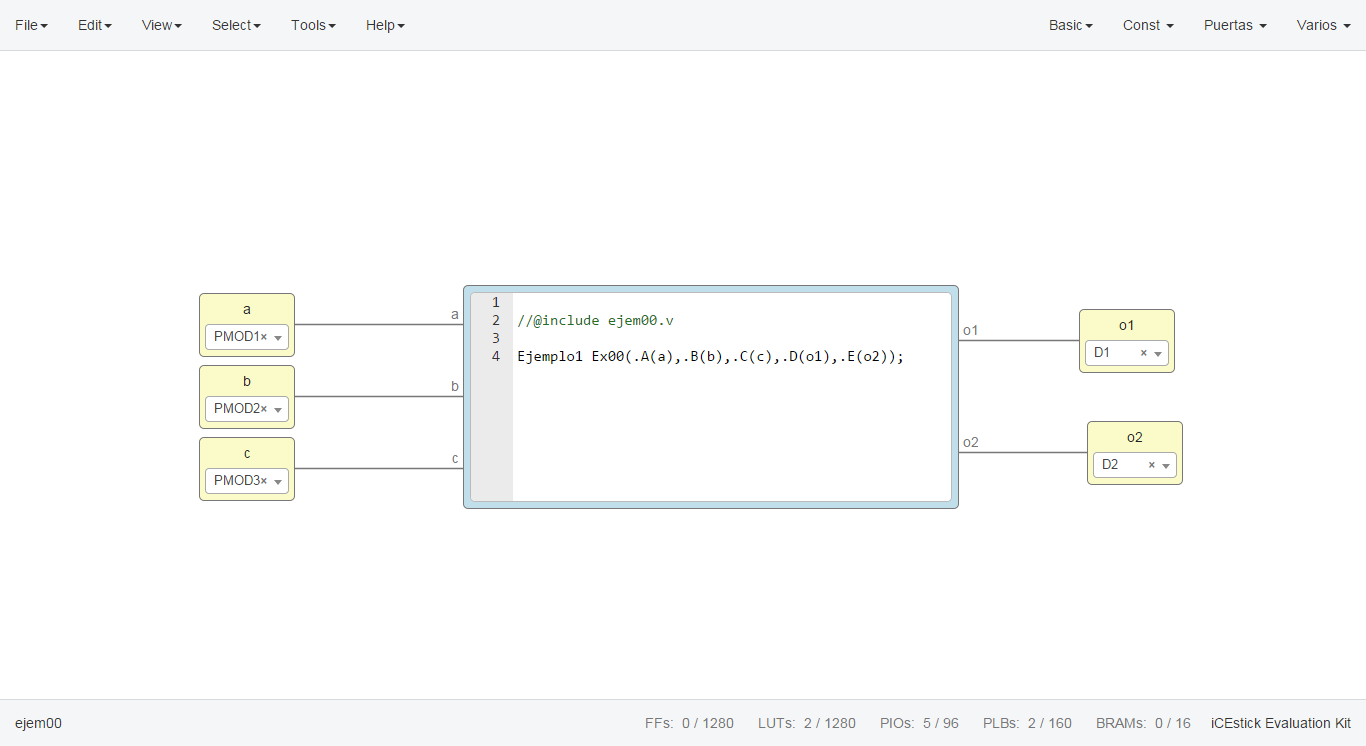

B. Una segunda forma de usar el código verilog, es directamente insertar el código empleando la directiva "include" añadiendo una primera línea a la caja de código de la siguiente forma:

// @include nombreFicheroVerilog.v

de esta forma se añade el código del fichero verilog y puede crearse una instancia del módulo dentro de la caja de código.

Podríamos por ejemplo crear un bloque de código usando el módulo verilog creado anteriormente ( module Ejemplo1 ) y que podríamos haber salvado en un fichero llamado ejem00.v de la forma:

ejem00.v

module Ejemplo1(A,B,C,D,E);

output D,E;

input A,B,C;

wire w1;

and G1(w1,A,B);

not G2(E,C);

or G3(D,w1,E);

endmodule

para ello creamos un bloque de código donde usamos la directiva include para referenciamos al fichero verilog ejem00.v que estará en el mismo directorio que nuestro fichero de icestudio *.ice que llamaremos por ejemplo ejem00.ice

donde creamos una instancia del módulo "Ejemplo1" llamado "Ex00" asociando las entradas,salidas del módulo "Ejemplo1" con las del módulo creado en nuestra caja de código.De esta forma, en este ejemplo podemos ver que las entradas a,b,c se corresponderán con las entradas A,B y C del módulo "Ejemplo1" y las salidas o1,o2 se corresponderán con las salidas del módulo "Ejemplo1" creado en el fichero de verilog "ejem00.v".

Visto esto, podemos resumir que podemos crear módulos propios desde el propio icestudio creando cajas de código o aprovechar ficheros de verilog *.v ya creados para incluirlos en las cajas de código de icestudio usando la directiva "//@include *.v" .

Podemos obtener los ficheros de ejemplo en el siguiente link: